# 1991 DATA BOOK UPDATE 1

**TECHNOLOGY AND CAPABILITIES**

2

**QUALITY AND RELIABILITY**

3

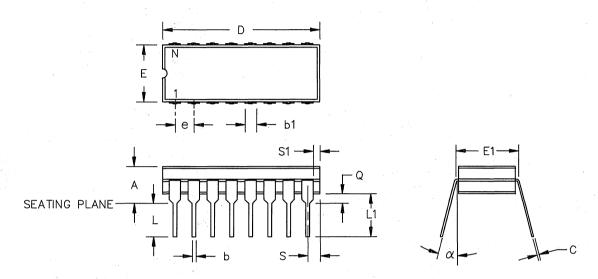

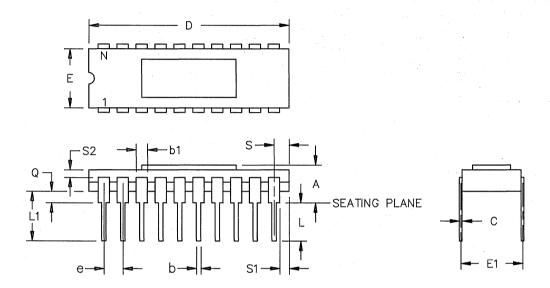

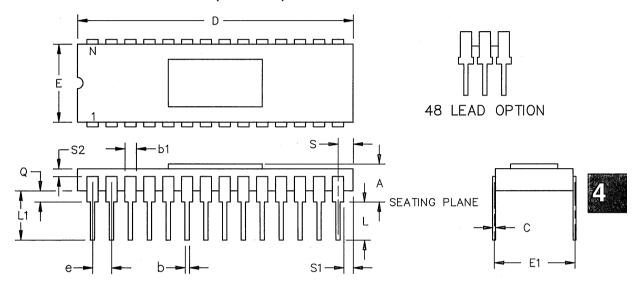

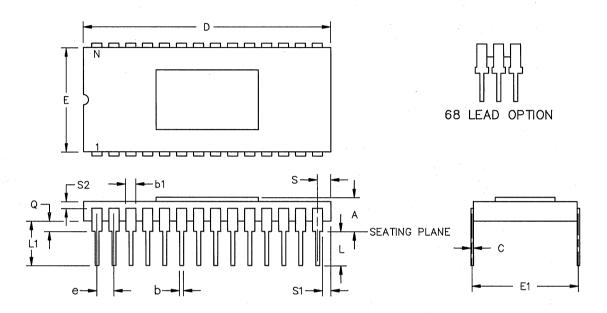

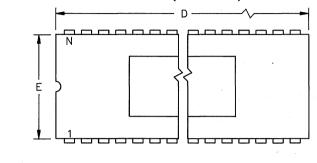

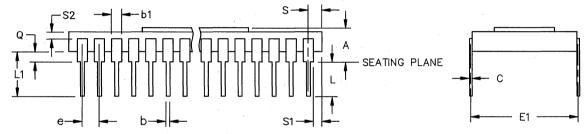

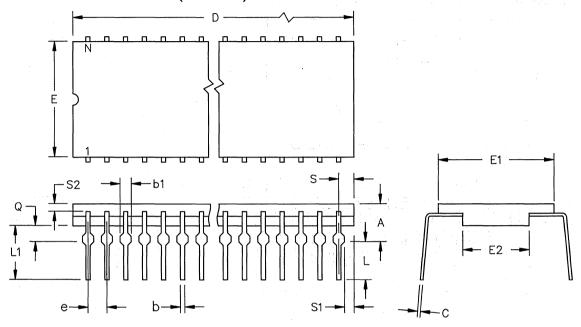

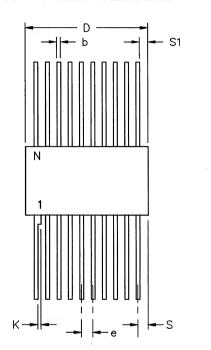

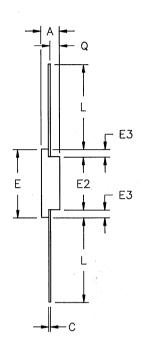

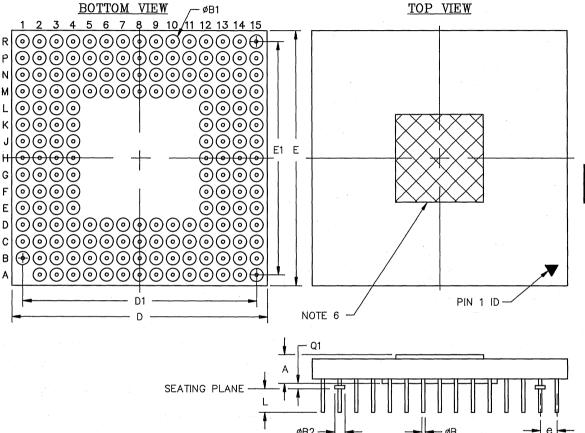

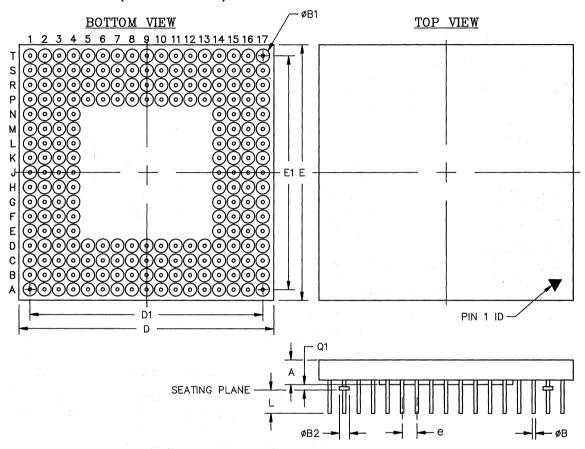

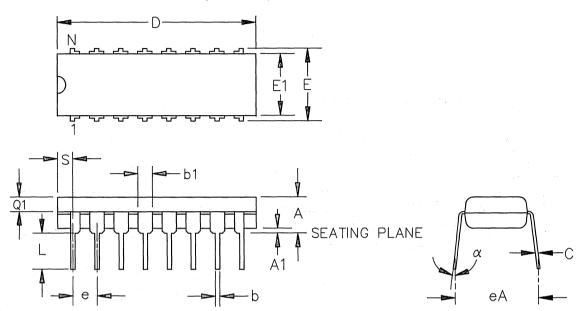

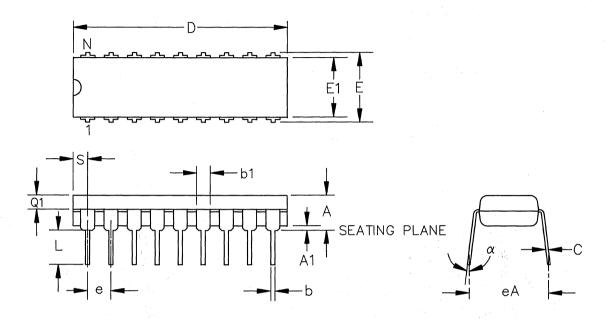

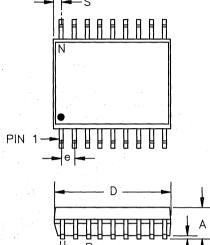

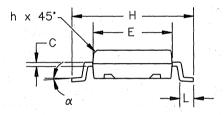

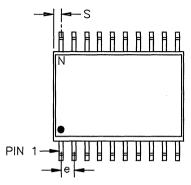

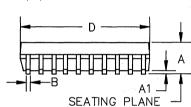

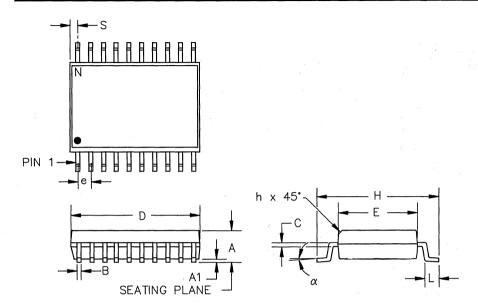

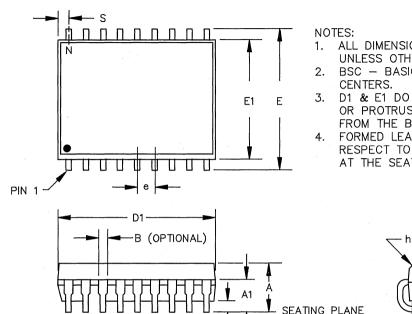

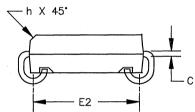

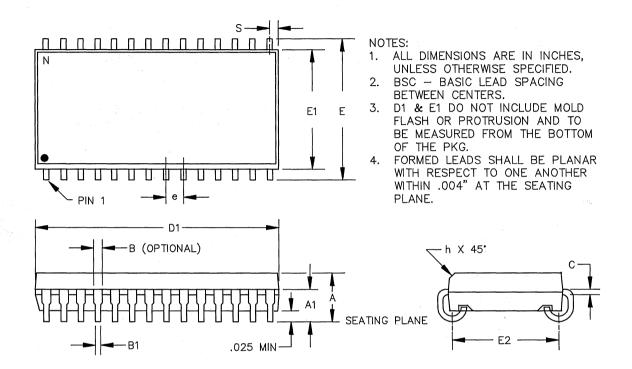

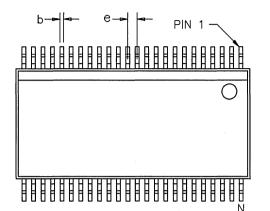

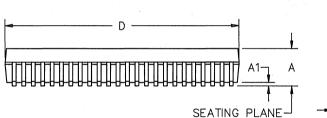

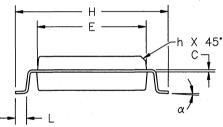

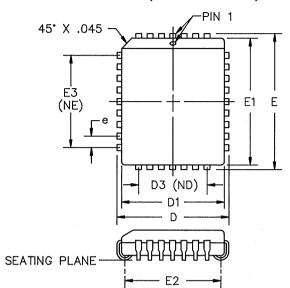

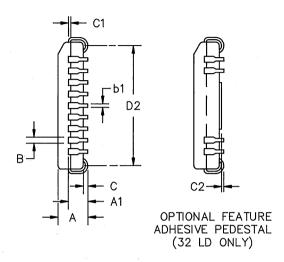

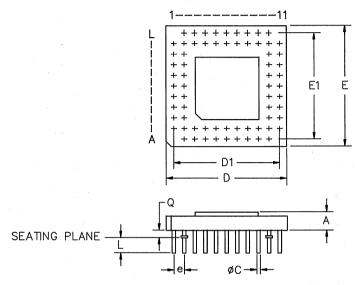

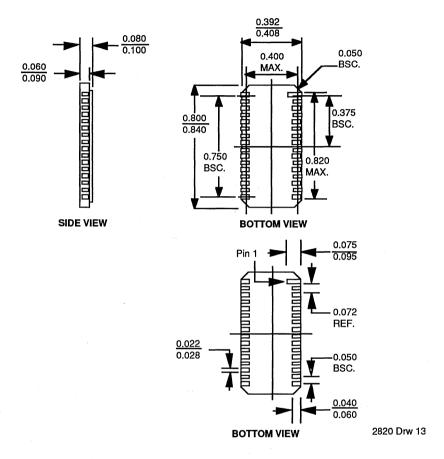

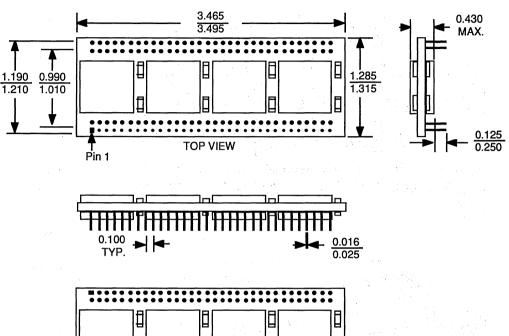

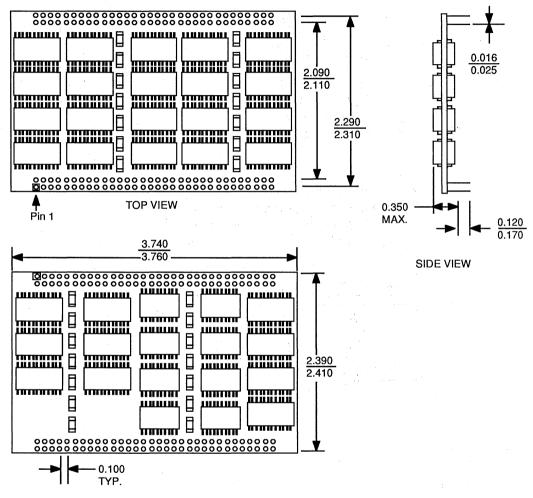

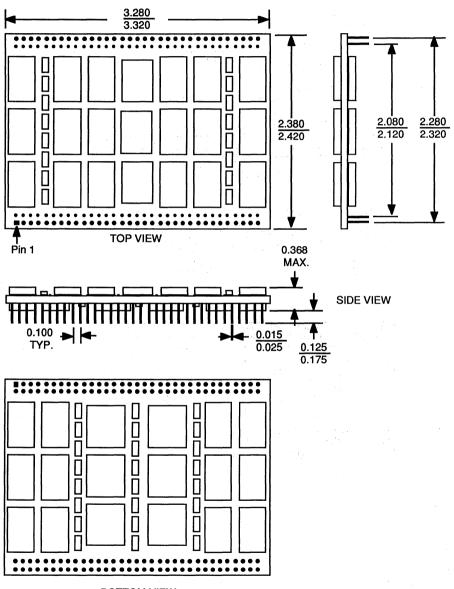

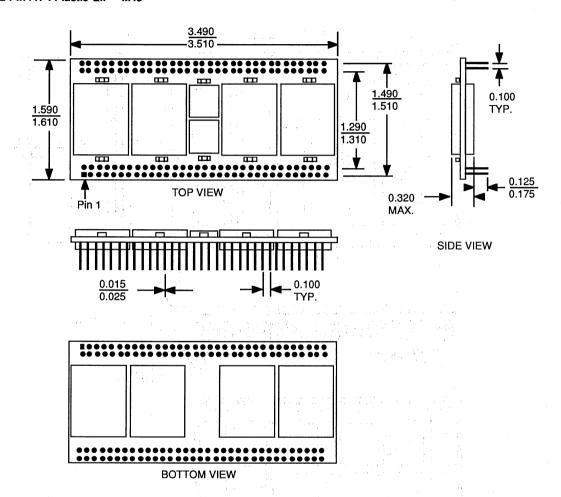

**PACKAGE DIAGRAM OUTLINES**

1990/1991 LOGIC DATA BOOK

A

1990/1991 SPECIALIZED MEMORIES DATA BOOK

3

1991 RISC DATA BOOK

1991 SRAW DATA BOOK

#### CONTENTS OVERVIEW

Historically, Integrated Device Technology has presented its product offerings entirely under one cover. In an effort to simplify this information for our customers, it has been divided into four separate data books — Logic, Specialized Memory, RISC and Static RAM.

This 1991 Update offers new and revised information from each of the four 1991 Data Books. Also included is a current, complete packaging section for all IDT product groups. This section will be updated in each subsequent data book.

The Table of Contents contains a listing of the products in the Update. All data sheets are designated by their corresponding Data Book (A = Logic, B = Specialized Memories, C = RISC, and D = Static RAM) and page numbered individually. For example, *Updated 1 C*, centered at the bottom of the page, refers to the 1991 RISC Data Book. The corresponding page number is shown in the lower right corner. New data sheets and application notes follow the partial and complete data sheets in the section with the data book that they will appear in when next published.

A header bar at the top of each change to a partial or complete data sheet indicates which 1990-91 data book the original data sheet can be found in. The reference is organized by data book, section and page number.

IDT, a recognized leader in high-speed CMOS technology, produces a broad line of products. This enables us to provide a complete CMOS solution to designers of high performance digital systems. Not only do our product lines include industry standard devices, they also feature products with faster speed, lower power, and package and/or architectural benefits that allow the designer to achieve significantly improved system performance.

**To find ordering information:** Start with the Ordering Information chart at the back of each **new** data sheet. Updated data sheets — for which only the updated information has been included — should be used in reference with the complete data sheet in the appropriate 1991 Data Book.

To find product data: Start with the Table of Contents, organized by data book (data books are organized with partially updated data sheets at the front, followed by updated full data sheets, then new data sheets) or with the numeric Table of Contents organized across all product lines. These indexes will direct you to the page(s) of the partial, full or new data sheet. Included in the update sections is a header bar above the change which has a reference for locating the complete data sheet in the appropriate 1991 Data Book. Data sheets may be of the following type:

**ADVANCE INFORMATION** — contain initial descriptions, subject to change, for products that are in development, including features and block diagrams.

**PRELIMINARY** — contain descriptions for products soon to be, or recently, released to production, including features, pinouts and block diagrams. Timing data are based on simulation or initial characterization and are subject to change upon full characterization.

**FINAL** — contain minimum and maximum limits specified over the complete supply and temperature range for full production devices.

New products, product performance enhancements, additional package types and new product families are being introduced frequently. Although this update is published in an effort to keep our customers informed of new and changing data, it is impossible for it to remain current. Please contact your local IDT sales representative to determine the latest device specifications, package types and product availability.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support

or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the

labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Note: Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

The IDT logo is a registered trademark, BUSMUX, Flexi-pak, BICEMOS, CacheRAM, CEMOS, Flow-thru EDC, IDT/ux, MacStation, REAL8, RISC SubSystem, RISController, RISCore, SmartLogic, SyncFIFO, TargetSystem, and R3051 are trademarks of Integrated Device Technology, Inc. FAST is a trademark of National Semiconductor Corporation. Intel and i486 are trademarks of Intel Corporation.

# 1

# 1991 DATA BOOK UPDATE 1 TABLE OF CONTENTS

|                        |                                                             |            | PAGE      |

|------------------------|-------------------------------------------------------------|------------|-----------|

| GENERAL INFORM         |                                                             |            |           |

|                        |                                                             |            | 1.1       |

| Table of Contents      |                                                             |            | 1.2       |

| Numeric Table of Conte | ents                                                        |            | 1.3       |

| TECHNOLOGY AN          | ID CAPABILITIES                                             |            | 2         |

| QUALITY AND RE         | LIABILITY                                                   |            | 3         |

| PACKAGE DIAGR          | AM OUTLINES                                                 |            |           |

| Package Diagram Outli  | ne Index                                                    |            | 4.2       |

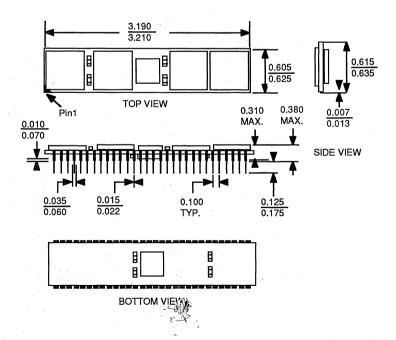

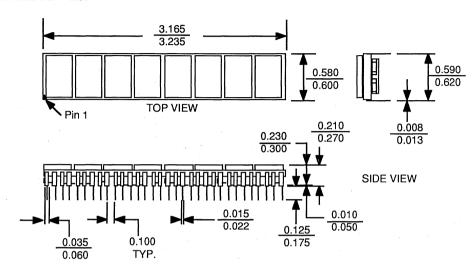

| Monolithic Package Dia | gram Outlines                                               |            | 4.3       |

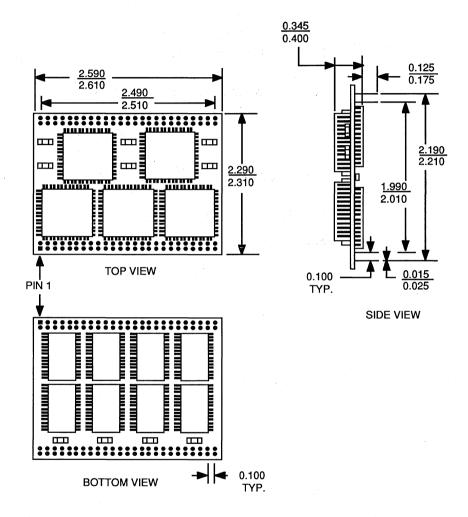

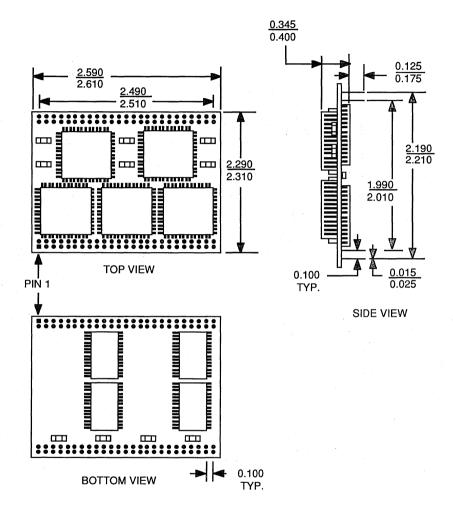

|                        | am Outlines                                                 |            |           |

|                        |                                                             | LAST BK. U | PDATE PG. |

| 1990/91 LOGIC DA       | TA BOOK UPDATES                                             | EACT DIX.  | i DATET G |

| PARTIALLY UPDATED      | D DATA SHEETS                                               |            |           |

| IDT54/74FCT240T        | Inverting Octal Buffer/Line Driver                          | A6.10      | A - 2     |

| IDT54/74FCT241T        | Inverting Octal Buffer/Line Driver                          | A6.10      | A - 2     |

| IDT54/74FCT244T        | Inverting Octal Buffer/Line Driver                          | A6.10      | A - 2     |

| IDT54/74FCT540T        | Inverting Octal Buffer/Line Driver                          | A6.10      | A - 2     |

| IDT54/74FCT541T        | Inverting Octal Buffer/Line Driver                          |            |           |

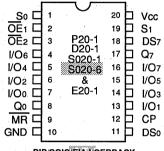

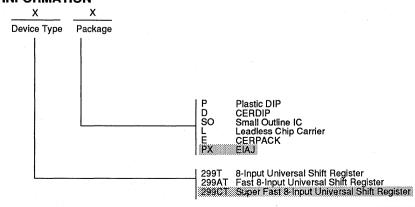

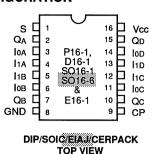

| IDT54/74FCT299T        | 8-Input Universal Shift Register w/Common Parallel I/O Pins | A6.13      | A - 3     |

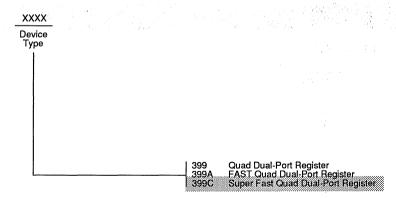

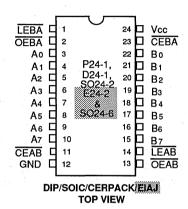

| IDT54/74FCT399T        | Quad Dual-Port Register                                     |            |           |

| IDT54/74FCT543T        | Non-inverting Octal Latched Transceiver                     |            |           |

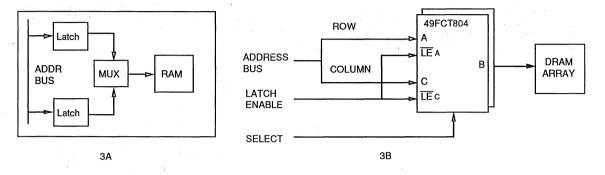

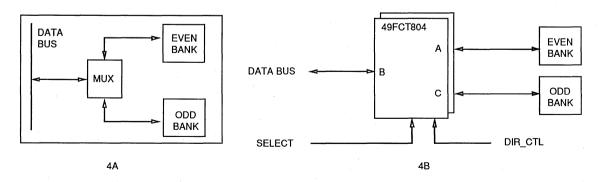

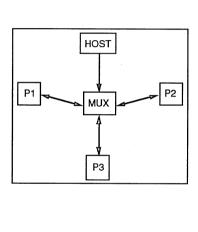

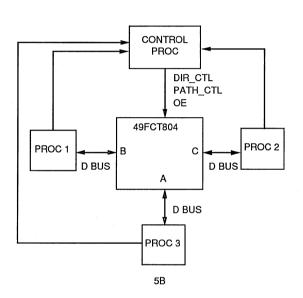

| IDT49FCT804            | High-Speed Tri-Port Bus Multiplexer                         | A6.29      | A - 6     |

| IDT54/74FCT240         | Inverting Octal Buffer/Line Driver                          | A6.40      | A - 8     |

| IDT54/74FCT241         | Inverting Octal Buffer/Line Driver                          | A6.40      | A - 8     |

| IDT54/74FCT244         | Inverting Octal Buffer/Line Driver                          |            |           |

| IDT54/74FCT540         | Inverting Octal Buffer/Line Driver                          |            |           |

| IDT54/74FCT541         | Inverting Octal Buffer/Line Driver                          |            |           |

| IDT54/74FCT299         | 8-Input Universal Shift Register w/Common Parallel I/O Pins |            |           |

| IDT54/74FCT399         | Quad Dual-Port Register                                     | A6.47      | A - 10    |

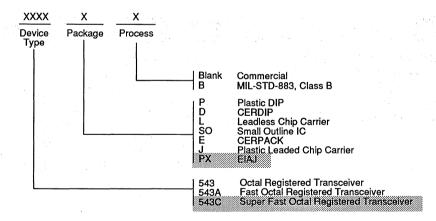

| IDT54/74FCT543         | Non-inverting Octal Latched Transceiver                     | A6.49      | A - 11    |

| UPDATED FULL DATA      | A SHEETS                                                    |            |           |

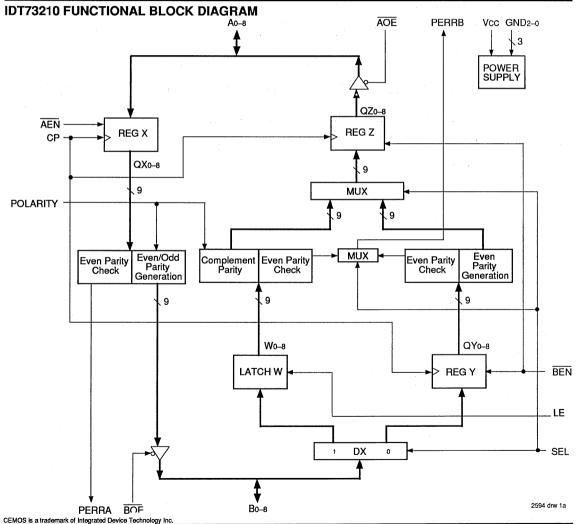

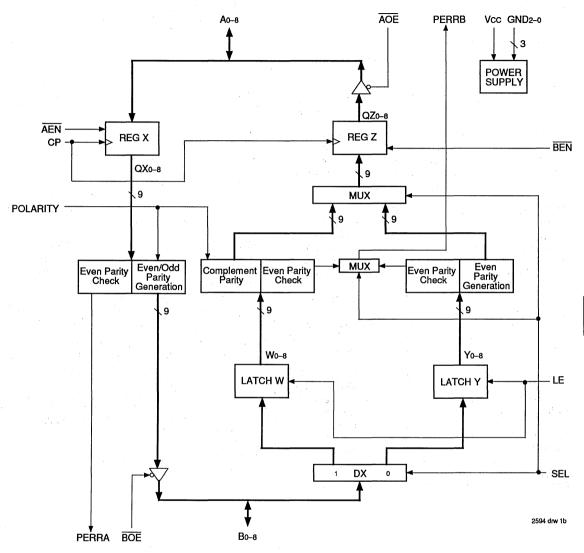

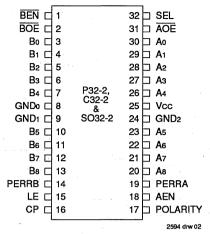

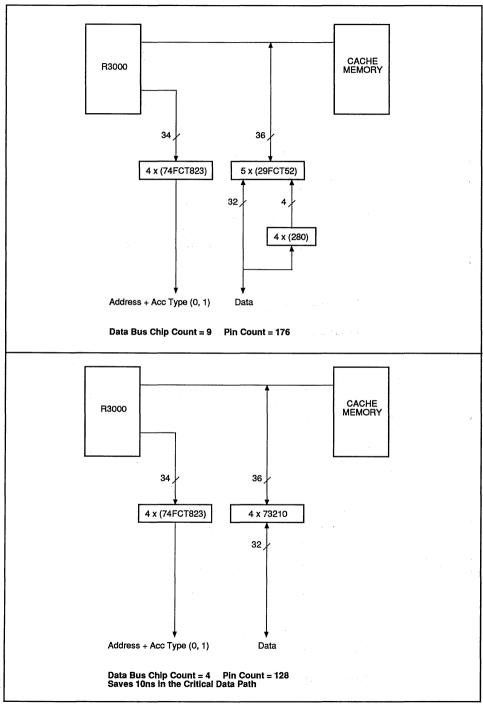

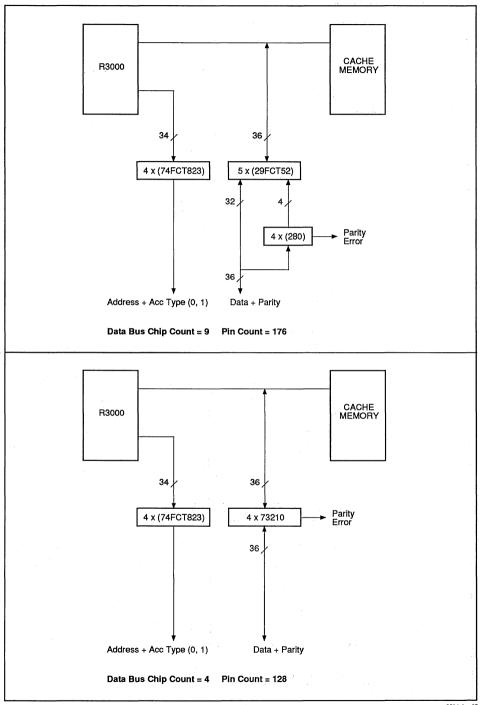

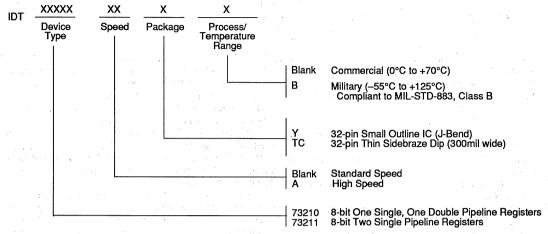

| IDT73210               | Fast Octal Register Transceiver w/Parity                    | A5.9       | A - 14    |

| IDT73211               | Fast Octal Register Transceiver w/Parity                    | A5.9       | A - 14    |

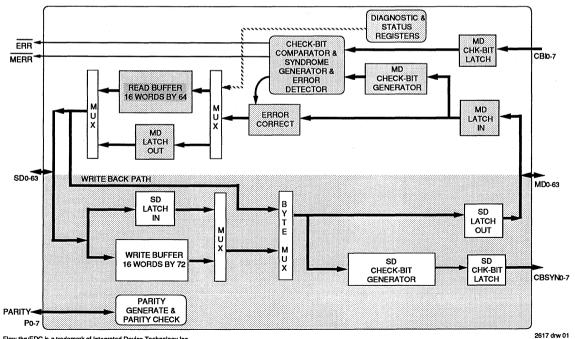

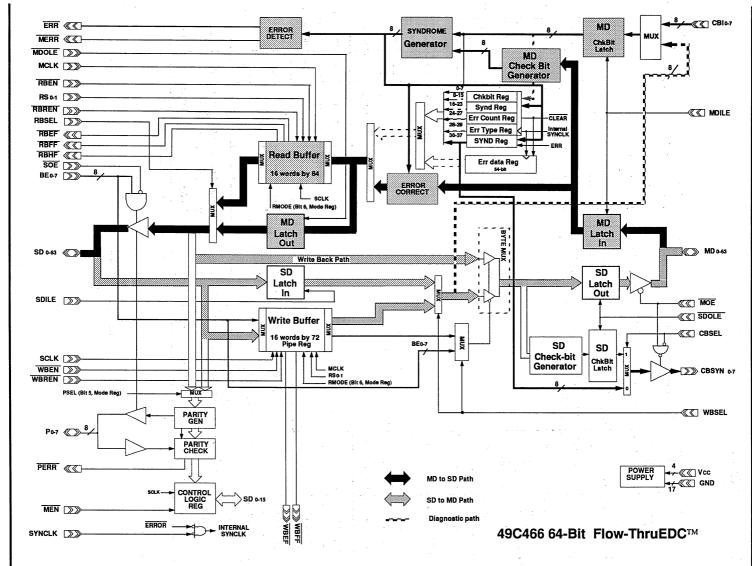

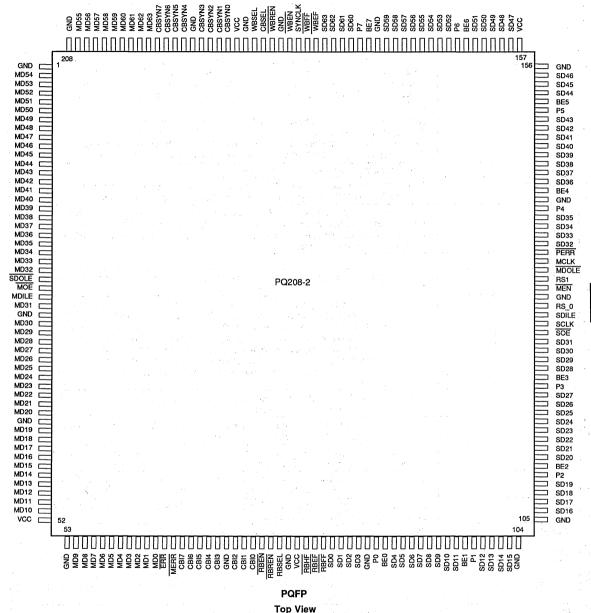

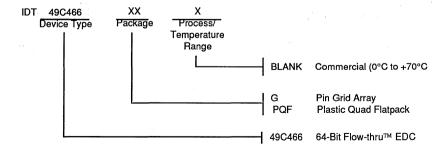

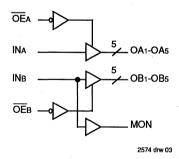

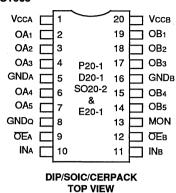

| IDT49C466              | 64-Bit CMOS Flow-ThruEDC Unit                               | A5.13      | A - 30    |

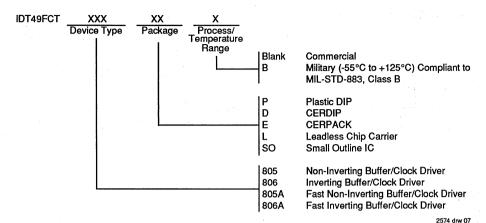

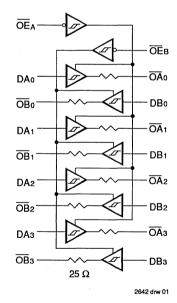

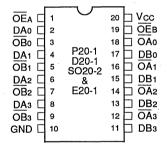

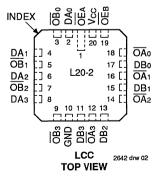

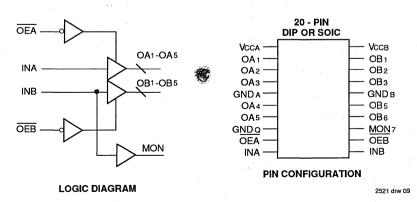

| IDT49FCT805A           | Buffer/Clock Driver w/Guaranteed Skew                       | A6.30      | A - 54    |

| IDT49FCT805            | Buffer/Clock Driver w/Guaranteed Skew                       | A6.30      | A - 54    |

| IDT49FCT806A           | Buffer/Clock Driver w/Guaranteed Skew                       | A6.30      | A - 54    |

| IDT49FCT806            | Buffer/Clock Driver w/Guaranteed Skew                       | A6.30      | A - 54    |

| IDT54/74FBT2240A       | Inverting Octal Buffer/Line Driver w/25Ω Series Resistor    | A6.67      | A - 61    |

| IDT54/74FBT2240        | Inverting Octal Buffer/Line Driver w/25Ω Series Resistor    | A6.67      | A - 61    |

| IDT54/74FBT2244A       | Inverting Octal Buffer/Line Driver w/25Ω Series Resistor    |            |           |

| IDT54/74FBT2244        | Inverting Octal Buffer/Line Driver w/25Ω Series Resistor    | A6.68      | A - 67    |

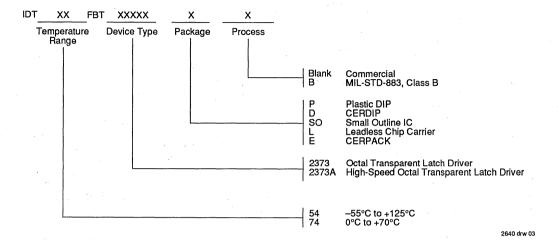

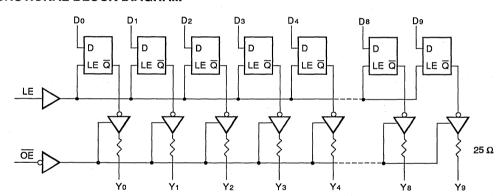

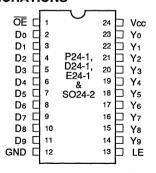

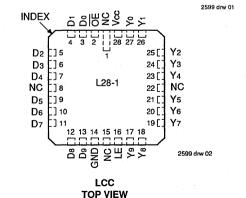

| IDT54/74FBT2373A       | Octal Transparent Latch w/3-State and 250 Series Resistor   | A6.69      | A - 73    |

|                        |                                                                   | LAST BK. U | JPDATE PG |

|------------------------|-------------------------------------------------------------------|------------|-----------|

|                        | TA BOOK UPDATES (Continued)                                       |            |           |

| UPDATED FULL DATA      |                                                                   | 40.00      | 4 70      |

| IDT54/74FBT2373        | Octal Transparent Latch w/3-State and 25Ω Series Resistor         |            |           |

| IDT54/74FBT2841A       | 10-Bit Memory Latch w/25Ω Series Resistor                         |            |           |

| IDT54/74FBT2841        | 10-Bit Memory Latch w/25Ω Series Resistor                         | . Ab./1    | . A-80    |

|                        | AND APPLICATION NOTES                                             |            |           |

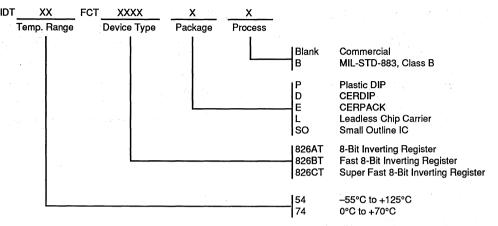

| IDT54/74FCT826T        | 8-Bit Inverting Register w/Multiple Enable                        |            | . A - 88  |

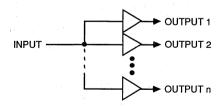

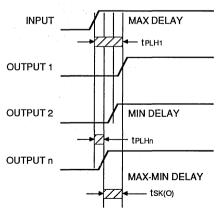

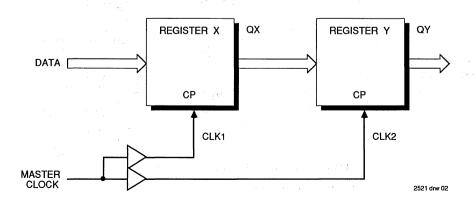

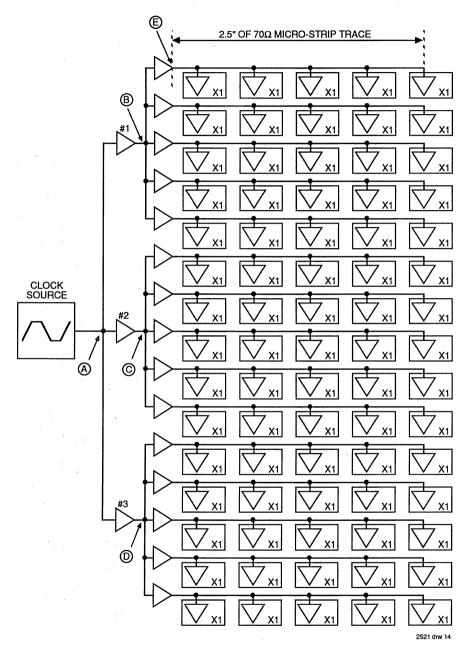

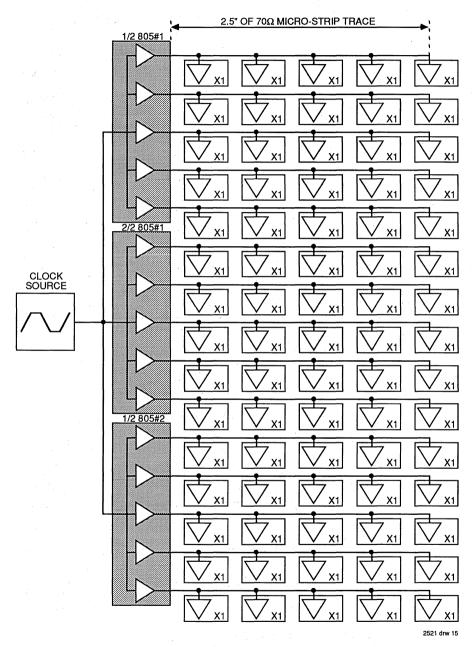

| AN-82                  | Clock Distribution Simplified w/IDT Guaranteed Skew Clock Drivers |            |           |

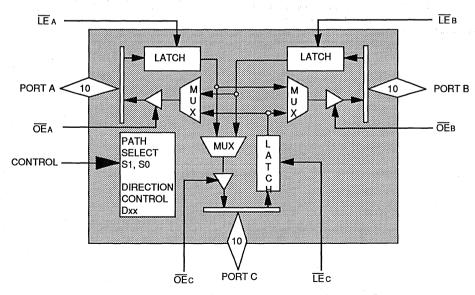

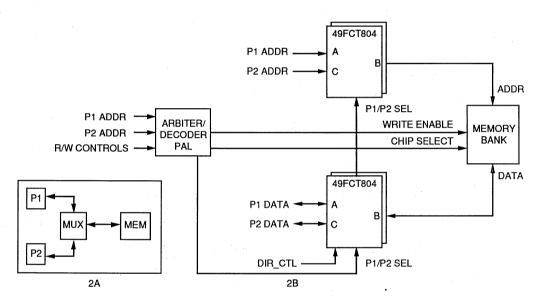

| AN-84                  | IDT49FCT804 Tri-Port Bus Multiplexer                              |            | . A - 106 |

| 1990/91 SPECIALIZ      | ZED MEMORIES DATA BOOK UPDATES                                    |            |           |

| PARTIALLY UPDATED      |                                                                   |            |           |

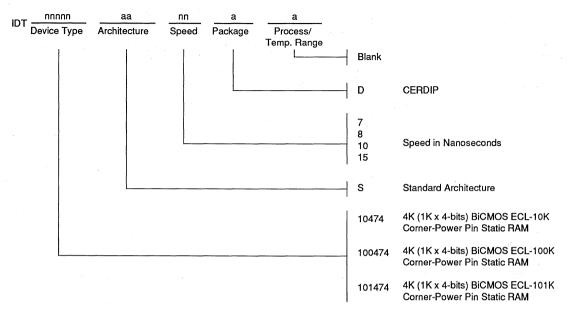

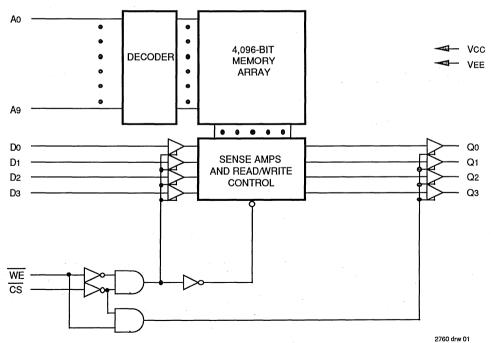

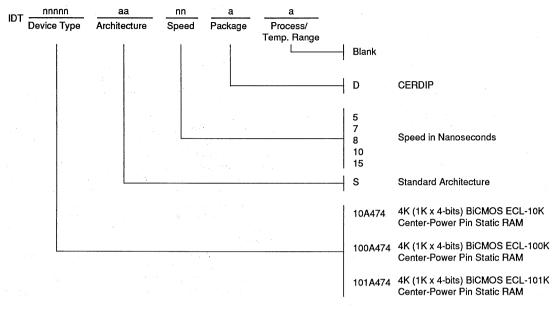

| IDT10484               | 4K x 4 ECL 10K SRAM (Corner Power)                                | R5 1       | B 2       |

| IDT10464               | 4K x 4 ECL 10K SRAM (Corner Power)                                |            |           |

| IDT100404<br>IDT101484 | 4K x 4 ECL 101K SRAM (Corner Power)                               |            |           |

| IDT101404              | 4K x 4 ECL 10K SRAM (Corner Power)                                |            |           |

| IDT10A464              | 4K x 4 ECL 10K SRAM (Corner Power)                                |            |           |

| IDT100A484             | 4K x 4 ECL 101K SRAM (Corner Power)                               |            |           |

| IDT1017484             | 64K x 1 ECL 10K SRAM                                              |            |           |

| IDT10490<br>IDT100490  | 64K x 1 ECL 100K SRAM                                             |            |           |

| IDT100490              |                                                                   |            |           |

|                        | 64K x 1 ECL 101K SRAM                                             |            |           |

| IDT10496RL             | 16K x 4 Self-Timed Reg Input, Latch Output                        |            |           |

| IDT100496RL            | 16K x 4 Self-Timed Reg Input, Latch Output                        |            |           |

| IDT101496RL            | 16K x 4 Self-Timed Reg Input, Latch Output                        |            |           |

| IDT10506RL             | 64K x 4 Self-Timed Reg Input, Latch Output                        |            |           |

| IDT100506RL            | 64K x 4 Self-Timed Reg Input, Latch Output                        |            |           |

| IDT101506RL            | 64K x 4 Self-Timed Reg Input, Latch Output                        |            |           |

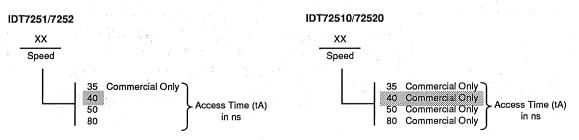

| IDT7251                | 512 x 18-Bit — 1K x 9-Bit BiFIFO                                  |            |           |

| IDT72510               | 512 x 18-Bit — 1K x 9-Bit BiFIFO                                  |            |           |

| IDT7252                | 512 x 18-Bit — 1K x 9-Bit BiFIFO                                  |            |           |

| IDT72520               | 512 x 18-Bit — 1K x 9-Bit BiFIFO                                  |            |           |

| IDT72511               | 512 x 18-Bit BiFIFO                                               |            |           |

| IDT72521               | 512 x 18-Bit BiFIFO                                               |            |           |

| IDT7030                | 8K (1K x 8) Dual-Port RAM (MASTER)                                |            |           |

| IDT7040                | 8K (1K x 8) Dual-Port RAM (SLAVE)                                 | . B7.2     | . B-8     |

| IDT7010                | 9K (1K x 9) Dual-Port RAM (MASTER)                                |            |           |

| IDT70104               | 9K (1K x 9) Dual-Port RAM (SLAVE)                                 |            |           |

| IDT7MB1006             | 64K x 16 Dual-Port Static RAM Module                              |            |           |

| IDT7MB1008             | 32K x 16 Dual-Port Static RAM Module                              |            |           |

| IDT7M1002              | 16K x 32 Dual-Port Static RAM Module                              |            |           |

| IDT7MP4034             | 256K x 8 CMOS Static RAM Module                                   | . B8.22    | . B - 17  |

| IDT7MB4040             | 256K x 9 CMOS Static RAM Module                                   |            |           |

| IDT7MC4032             | 16K x 32 CMOS Static RAM Module w/Separate Data I/O               |            |           |

| IDT7MP4031             | 16K x 32 CMOS Static RAM Module                                   | . B8.36    | . B - 20  |

| IDT7MP4036             | 64K x 32 CMOS Static RAM Module                                   | . B8.39    | . B - 21  |

| IDT7MP4045             | 256K x 32 CMOS Static RAM Module                                  | . B8.40    | . B - 22  |

| UPDATED FULL DATA      | A SHEETS                                                          |            |           |

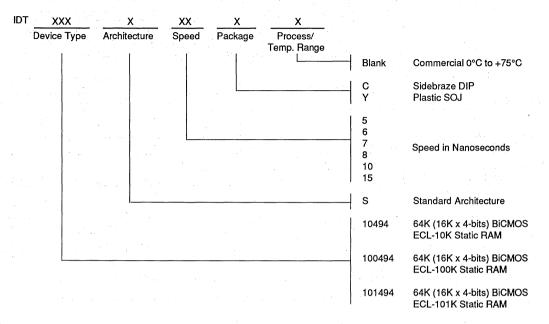

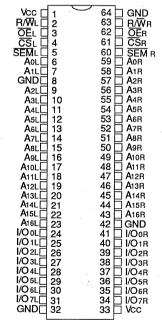

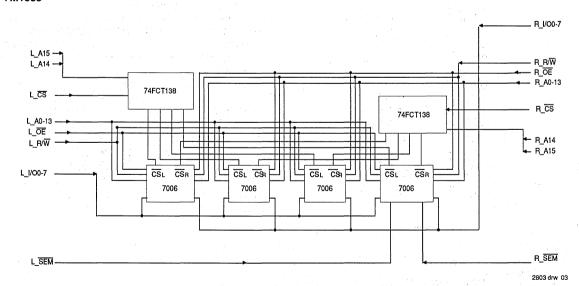

| IDT10494               | 16K x 4 ECL 10K SRAM                                              |            | . B - 26  |

| IDT100494              | 16K x 4 ECL 100K SRAM                                             |            |           |

| IDT101494              | 16K x 4 ECL 101K SRAM                                             |            |           |

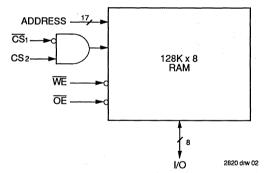

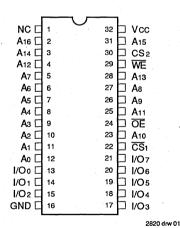

| IDT7M1001              | 128K x 8 Dual-Port Static RAM Module                              |            |           |

| IDT7M1001              | 64K x 8 Dual-Port Static RAM Module                               |            |           |

| IDT7M1003              | 512K x 16 CMOS Static RAM Module                                  |            |           |

| DITINI TOTI            | OTEN A TO OMOG OLIGIO FIRM MODULE                                 | . 50.07,   | . 2 00    |

UPDATE 1 1.2 2

| 1990/91 SPECIALIZE     | D MEMORIES DATA BOOK UPDATES (Continued)                                           |    |      |

|------------------------|------------------------------------------------------------------------------------|----|------|

| NEW DATA SHEETS AND    |                                                                                    |    |      |

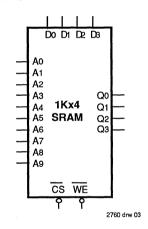

| IDT10474               | 1K x 4 ECL 10K SRAM                                                                | В٠ | - 58 |

| IDT100474              | 1K x 4 ECL 100K SRAM                                                               | В٠ | - 58 |

| IDT101474              | 1K x 4 ECL 101K SRAM                                                               | В٠ | - 58 |

| IDT10A474              | 1K x 4 ECL 10K SRAM                                                                | В- | - 67 |

| IDT100A474             | 1K x 4 ECL 100K SRAM                                                               | В  | - 67 |

| IDT101A474             | 1K x 4 ECL 101K SRAM                                                               | В- | - 67 |

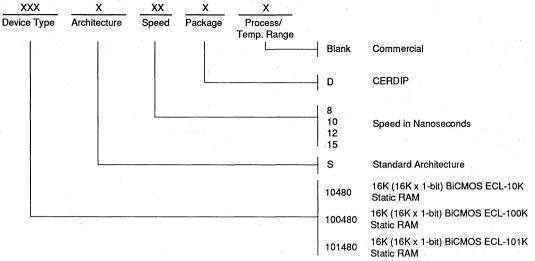

| IDT10480               | 16K x 1 ECL 10K SRAM                                                               | В٠ | - 76 |

| IDT100480              | 16K x 1 ECL 10K SRAM                                                               |    |      |

| IDT101480              | 16K x 1 ECL 10K SRAM                                                               | В٠ | - 76 |

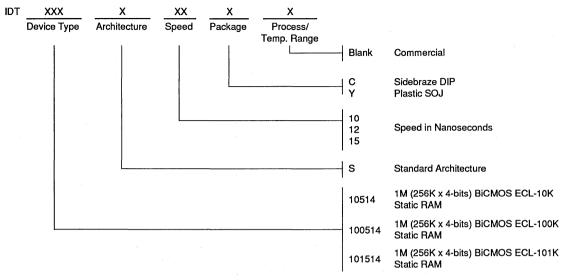

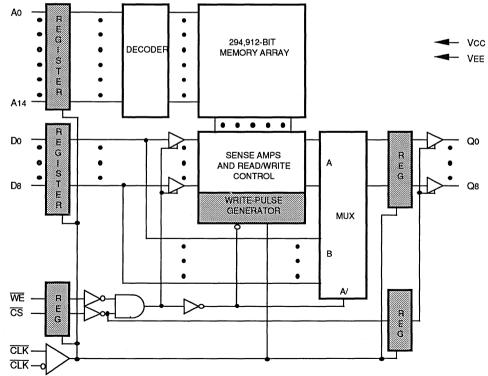

| IDT10514               | 256K x 4 ECL 10K SRAM                                                              | В٠ | - 85 |

| IDT100514              | 256K x 4 ECL 10K SRAM                                                              | B- | - 85 |

| IDT101514              | 256K x 4 ECL 10K SRAM                                                              | В٠ | - 85 |

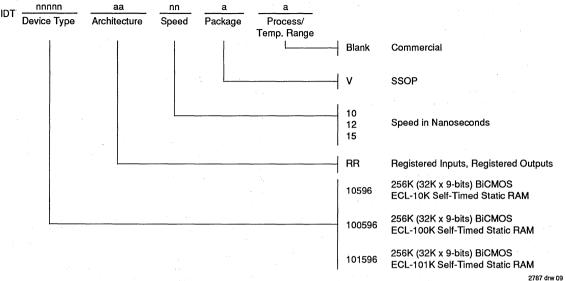

| IDT10596RR             | 32K x 9 ECL 10K SRAM                                                               | В٠ | - 94 |

| IDT100596RR            | 32K x 9 ECL 10K SRAM                                                               | В- | - 94 |

| IDT101596RR            | 32K x 9 ECL 10K SRAM                                                               | В- | - 94 |

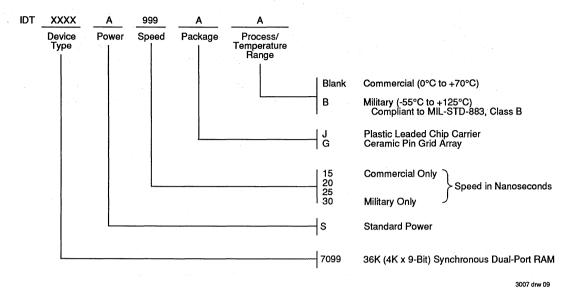

| IDT7099                | 36K (4K x 9-Bit) Synchronous Dual-Port RAM                                         |    |      |

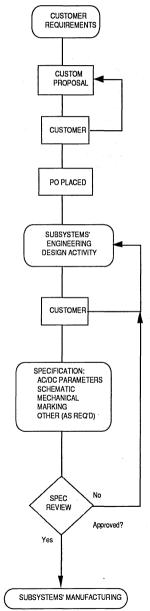

| Subsystems Custom Modu | ule Capabilities                                                                   |    |      |

| IDT71M024              | 128K x 8 CMOS Static RAM Module                                                    |    |      |

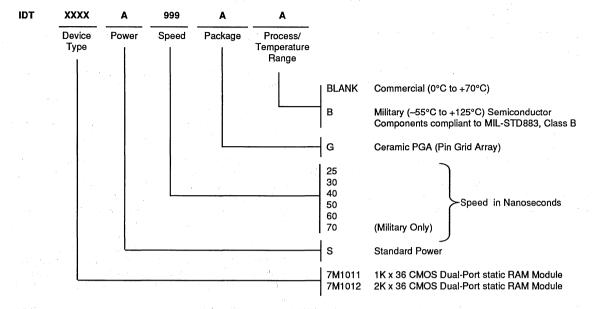

| IDT7M1011              | 1K x 36 CMOS Dual-Port Static RAM Module                                           |    |      |

| IDT7M1012              | 2K x 36 CMOS Dual-Port Static RAM Module                                           |    |      |

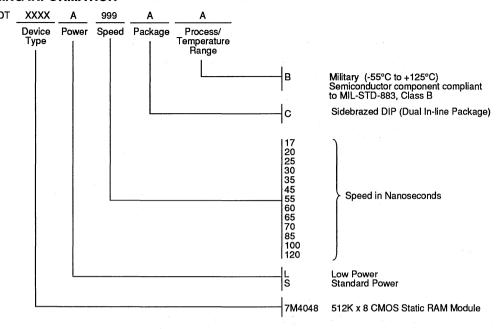

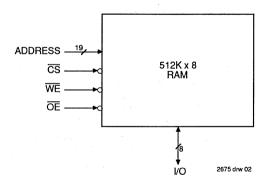

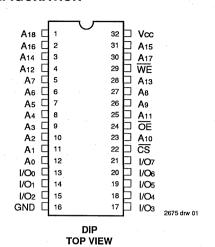

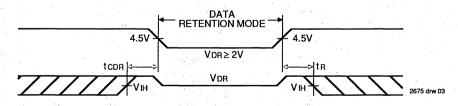

| IDT7M4048              | 512 x 8 CMOS Static RAM Module — Military                                          |    |      |

| IDT7M4048              | 512 x 8 CMOS Static RAM Module — Commercial                                        |    |      |

| IDT7MB4048             | 512 x 8 CMOS Static RAM Module — Commercial                                        |    |      |

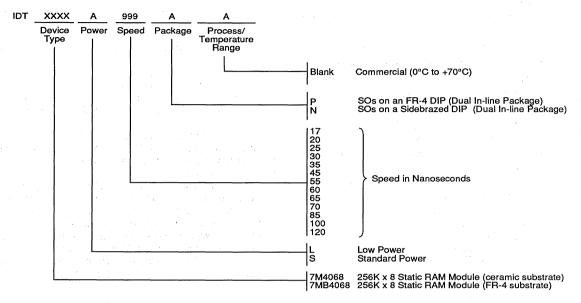

| IDT7M4068              | 256K x 8 CMOS Static RAM Module — Military                                         |    |      |

| IDT7M4068              | 256K x 8 CMOS Static RAM Module — Commercial                                       |    |      |

| IDT7MB4068             | 256K x 8 CMOS Static RAM Module — Commercial                                       |    |      |

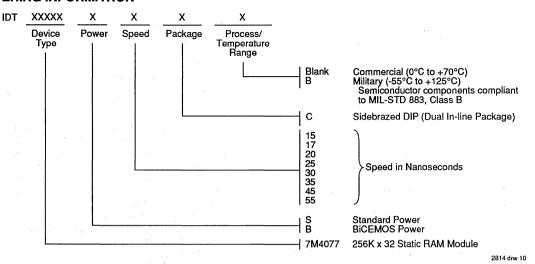

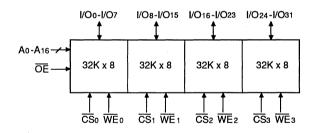

| IDT7M4077              | 256K x 32 BiCMOS/CMOS Static RAM Module                                            |    |      |

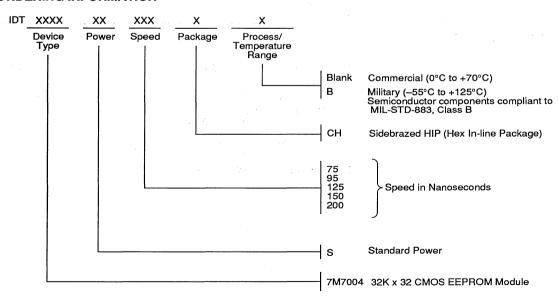

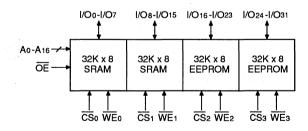

| IDT7M7004              | 32K x 32 CMOS EEPROM Module                                                        |    |      |

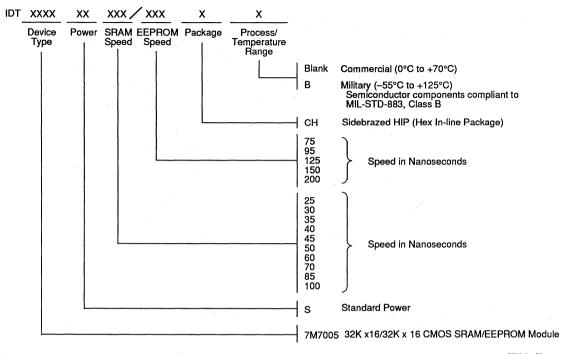

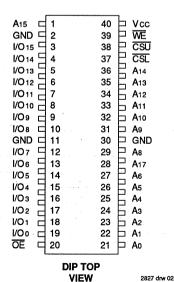

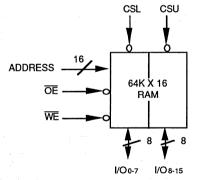

| IDT7M7005              | 32K x 16 SMOS SRAM/EEPROM Module                                                   |    |      |

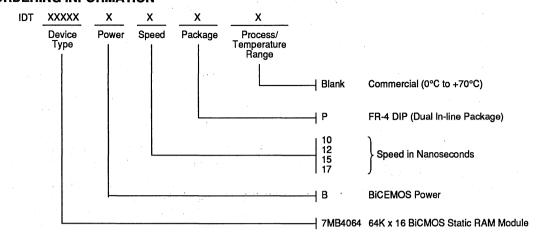

| IDT7MB4064             | 64K x 16 BiCMOS Static RAM Module                                                  |    |      |

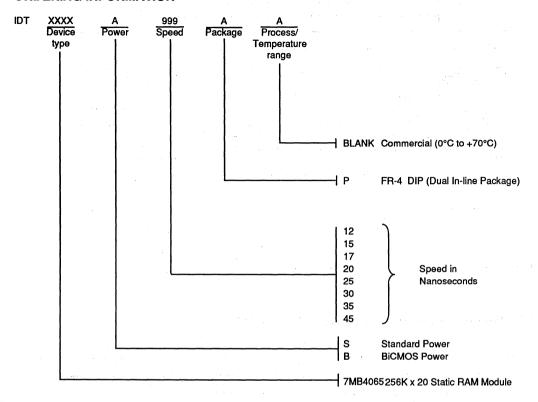

| IDT7MB4065             | 256K x 20 BiCMOS/CMOS Static RAM Module                                            |    |      |

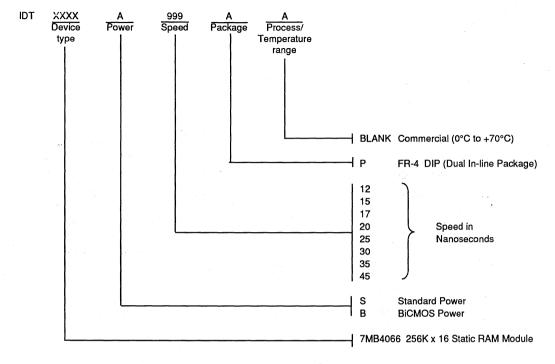

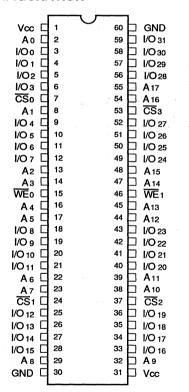

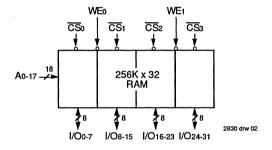

| IDT7MB4066             | 256K x 16 BiCMOS/CMOS Static RAM Module                                            |    |      |

| IDT7MB4067             | 256K x 32 CMOS Static RAM Module                                                   |    |      |

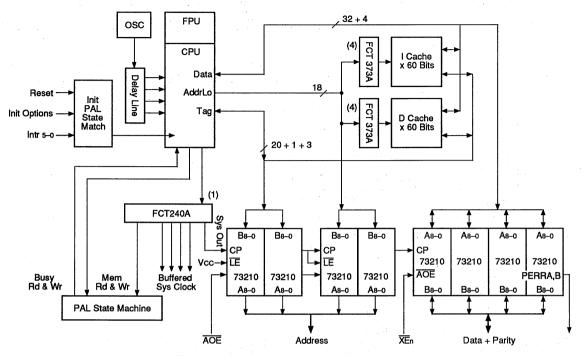

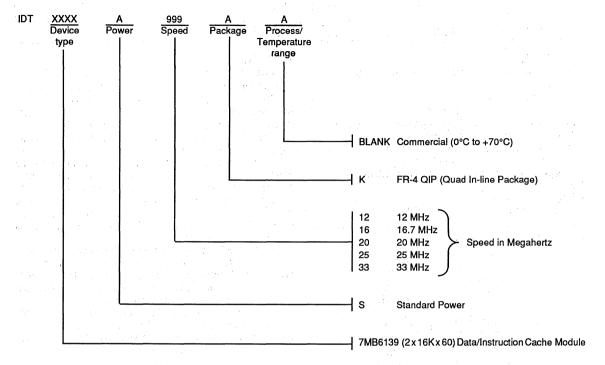

| IDT7MB6139             | Dual (16K x 60) Data/Instruction Cache Module for IDT79R3000 CPU                   |    |      |

| IDT7MP1021             | 128K x 8 CMOS Dual-Port Static RAM Module                                          |    |      |

| IDT7MP1023             | 64K x 8 CMOS Dual-Port Static RAM Module                                           |    |      |

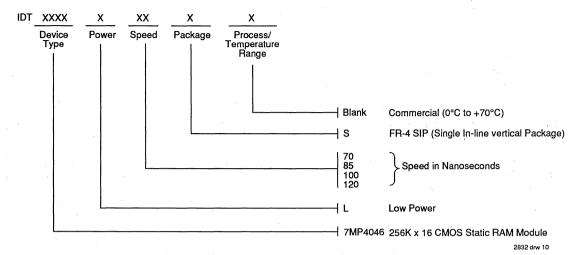

| IDT7MP4046             | 256K x 16 CMOS Static RAM Module                                                   |    | -    |

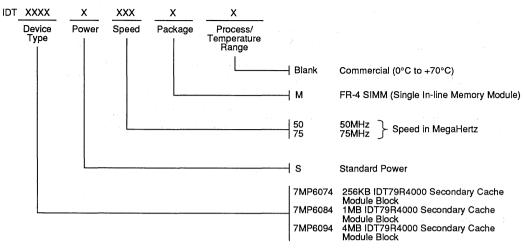

| IDT7MP6074             | 256K IDT79R4000 Secondary Cache Module Block Family                                |    |      |

| DT7MP6084              | 1MB IDT79R4000 Secondary Cache Module Block Family                                 |    |      |

| IDT7MP6094             | 4MB IDT79R4000 Secondary Cache Module Block Family                                 |    |      |

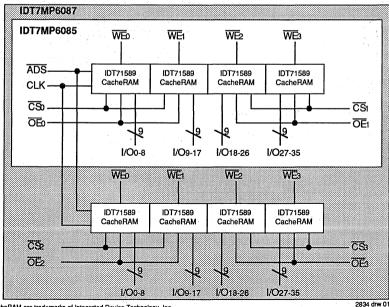

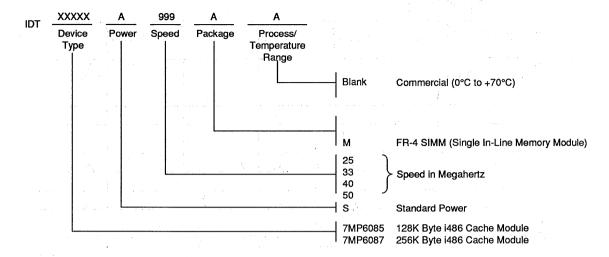

| DT7MP6085              | 128K Byte CMOS Secondary Cache Module for the Intel™ i486™                         |    |      |

| DT7MP6087              | 256K Byte CMOS Secondary Cache Module for the Intel <sup>™</sup> i486 <sup>™</sup> |    |      |

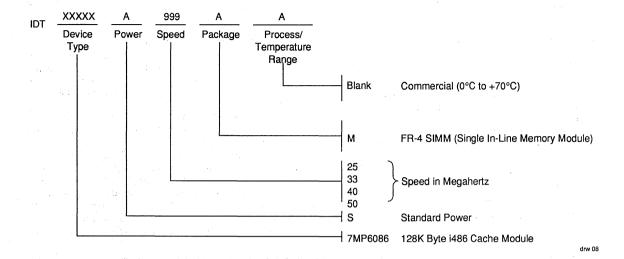

| DT7MP6086              | 128K Byte CMOS Secondary Cache Module for the Intel™ i486™                         |    |      |

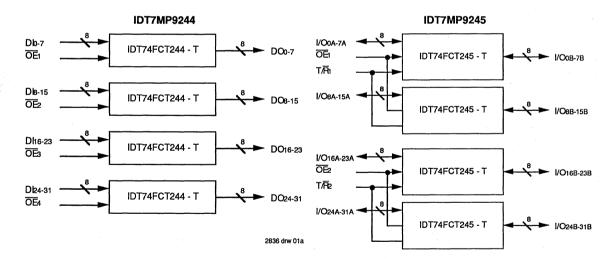

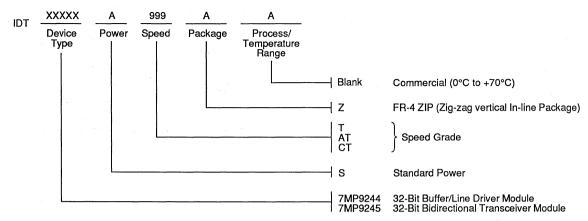

| DT7MP9244AT            | Fast CMOS 32-Bit Buffer/Line Driver and Bidirectional Transceiver Modules          |    |      |

| DT7MP9244CTZ           | Fast CMOS 32-Bit Buffer/Line Driver and Bidirectional Transceiver Modules          |    |      |

| DT7MP9244T             | Fast CMOS 32-Bit Buffer/Line Driver and Bidirectional Transceiver Modules          |    |      |

| DT7MP9245AT            | Fast CMOS 32-Bit Buffer/Line Driver and Bidirectional Transceiver Modules          |    |      |

| DT7MP9245CTZ           | Fast CMOS 32-Bit Buffer/Line Driver and Bidirectional Transceiver Modules          |    |      |

| DT7MP9245T             | Fast CMOS 32-Bit Buffer/Line Driver and Bidirectional Transceiver Modules          |    |      |

|                        | k™" CMOS Module Family                                                             |    |      |

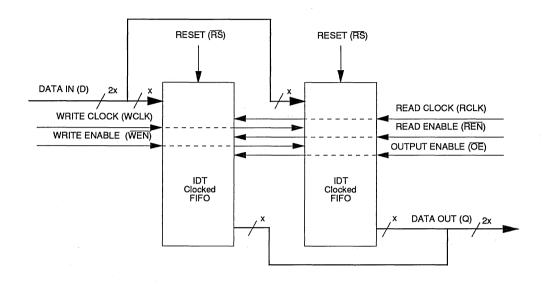

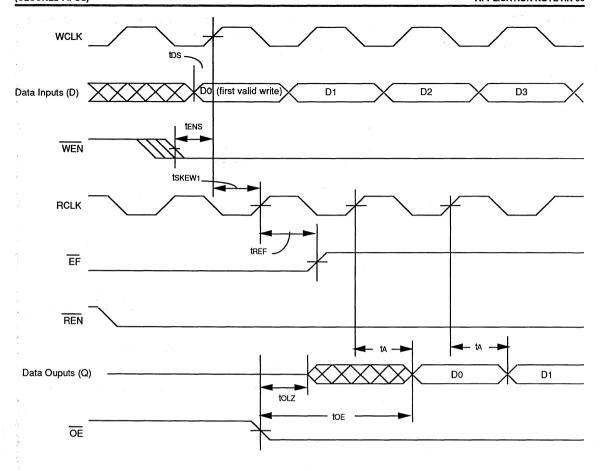

| AN-83                  | Width Expansion of SyncFIFOs™ (Clocked FIFOs)                                      |    |      |

| 55                     | The Lapandon of Opinion to Colonol I ii Ooj                                        |    | -0-  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LAST BK.                                | JPDATE PG |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------|

| 1991 RISC DATA BO         | OOK UPDATES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         |           |

| PARTIALLY UPDATED I       | DATA SHEETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         | 4         |

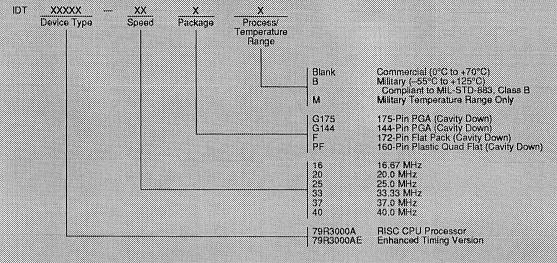

| IDT79R3000A               | RISC CPU Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C5.1                                    | C-2       |

| IDT79R3000AE              | RISC CPU Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |           |

| IDT79R3010A               | RISC Floating Point Accelerator (FPA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | C5.3                                    | C-4       |

| IDT79R3010AE              | RISC Floating Point Accelerator (FPA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | C5.3                                    | C-4       |

| IDT7RS107                 | R3000 CPU Modules for High Performance and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |           |

|                           | MultiProcessor Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | C7.5                                    | C - 5     |

| IDT7RS108                 | R3000 CPU Modules with 256K Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C7.6                                    | C-8       |

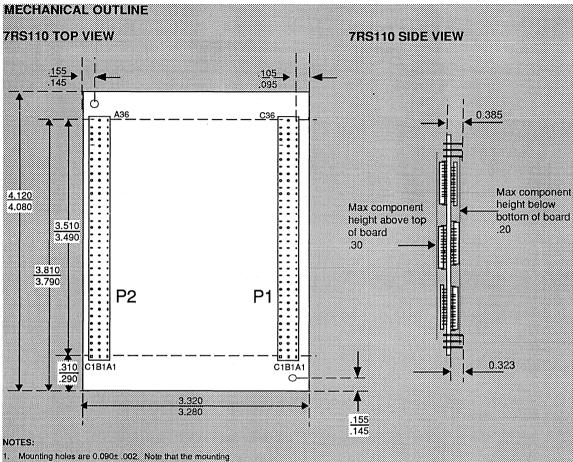

| IDT7RS110                 | Plug Compatible Family of R3000 CPU Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | C7.8                                    | C - 11    |

| UPDATED FULL DATAS        | SHEETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                         |           |

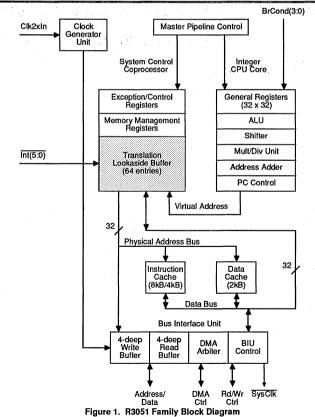

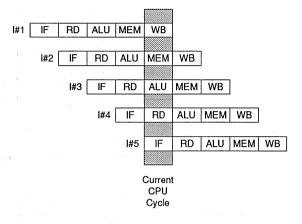

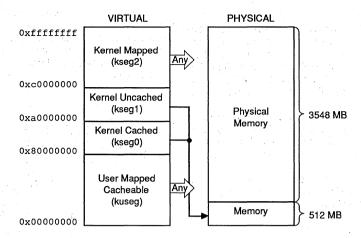

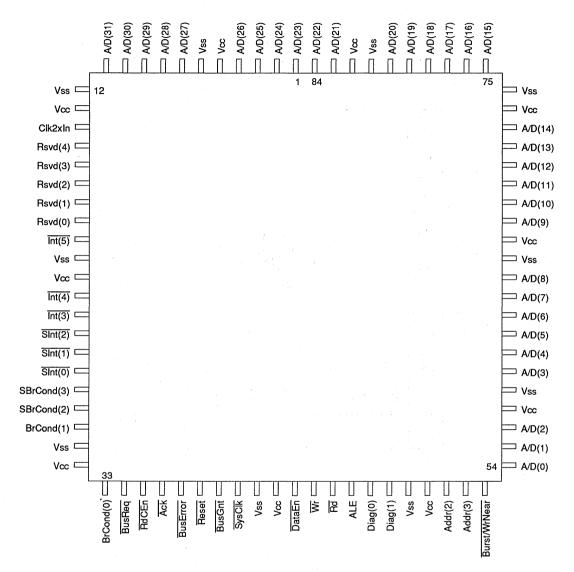

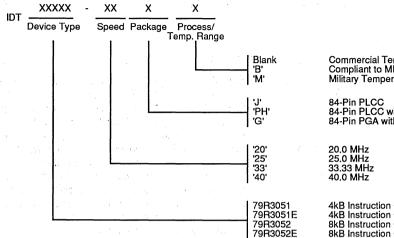

| IDT79R3051                | IDT79R3051 Family of Integrated RISControllers™                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C5.5                                    | C - 16    |

| IDT79R3052                | IDT79R3051 Family of Integrated RISControllers™                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |           |

| IDT7RS109                 | R3000 CPU Modules with 256K Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |           |

| IDT7RS901                 | IDT/sim System Integration Manager ROMable Debugging Kernal .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         |           |

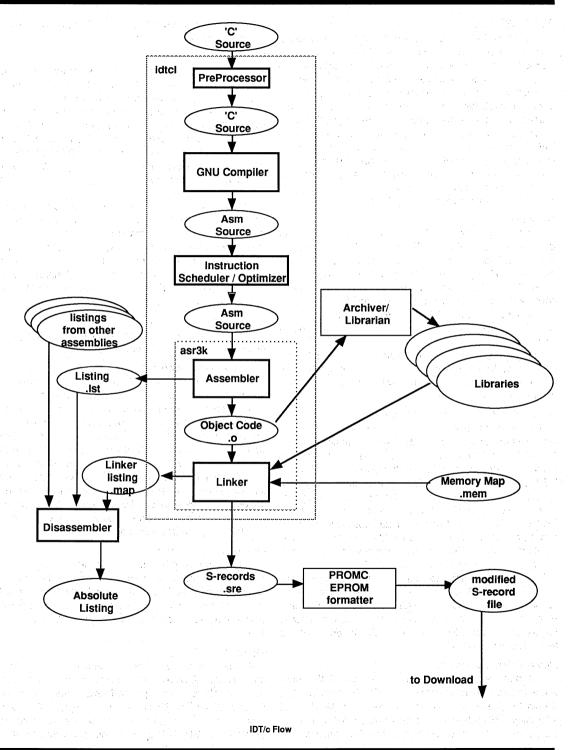

| IDT7RS903                 | IDT/c Multi-Host C-Compiler System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |           |

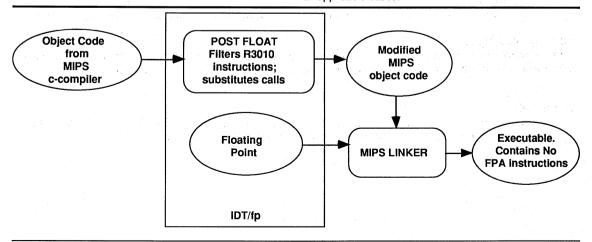

| IDT7RS905                 | IDT/fp Floating Point Library for Use with R3000 Compilers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |           |

| 15 11 11 10 10 10         | To the Floating Found Elbrary for Coo With Floods Compilers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | · · · · · · · · · · · · · · · · · · ·   | 0 02      |

| <b>NEW APPLICATION NO</b> | TES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         |           |

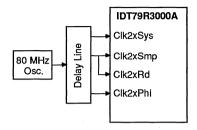

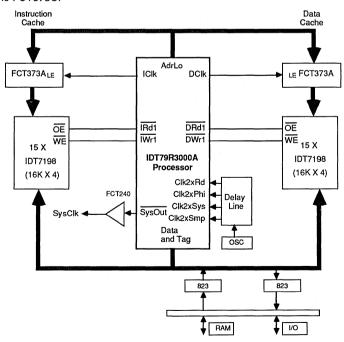

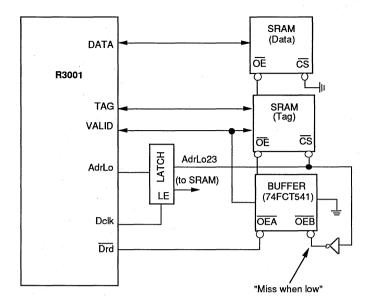

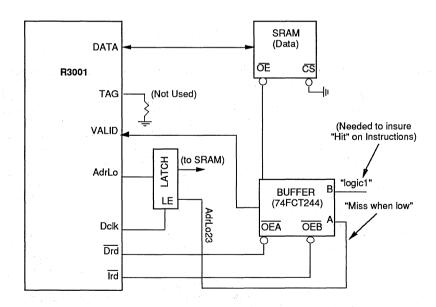

| AN-85                     | SRAM Timing Parameters for 40MHz R3000A Cache Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         | C - 66    |

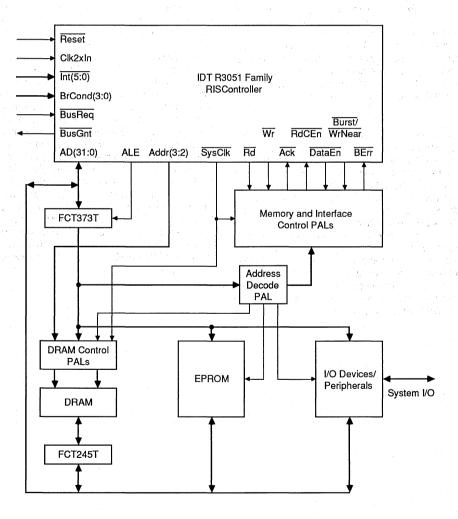

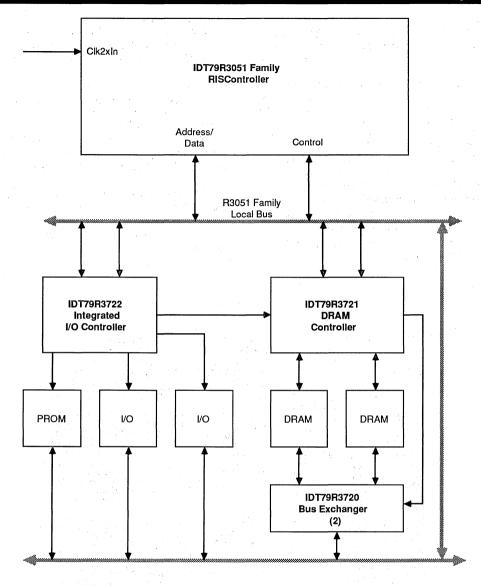

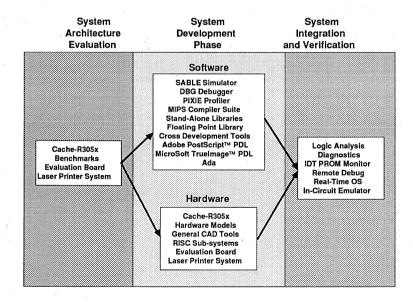

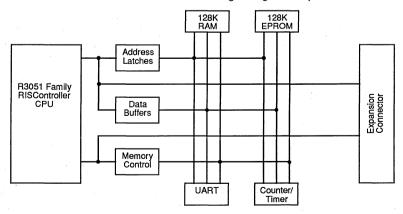

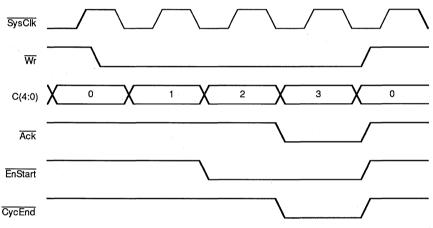

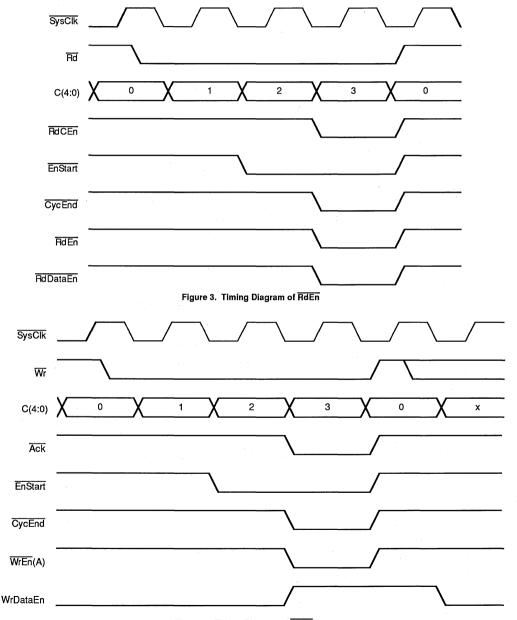

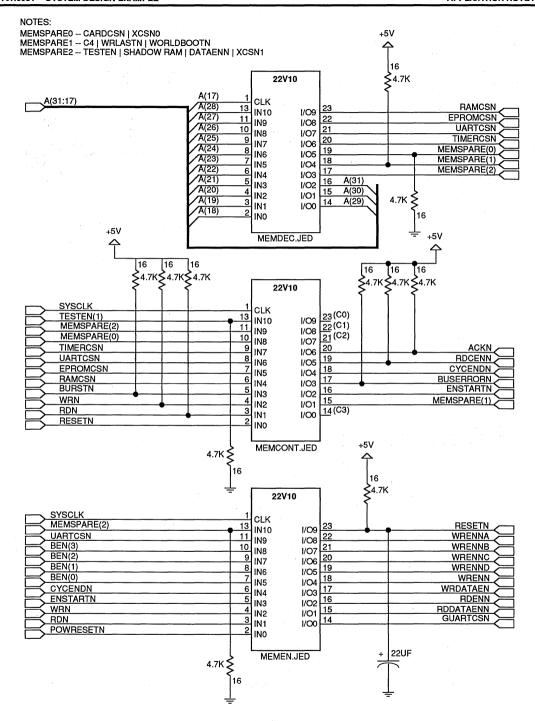

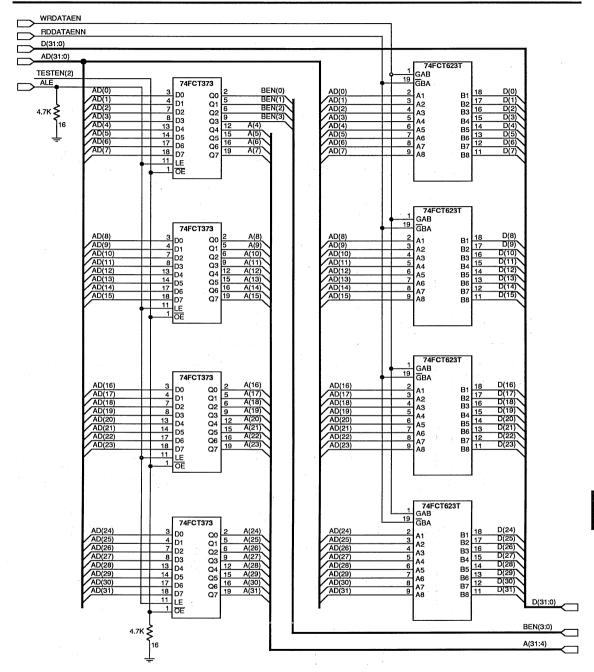

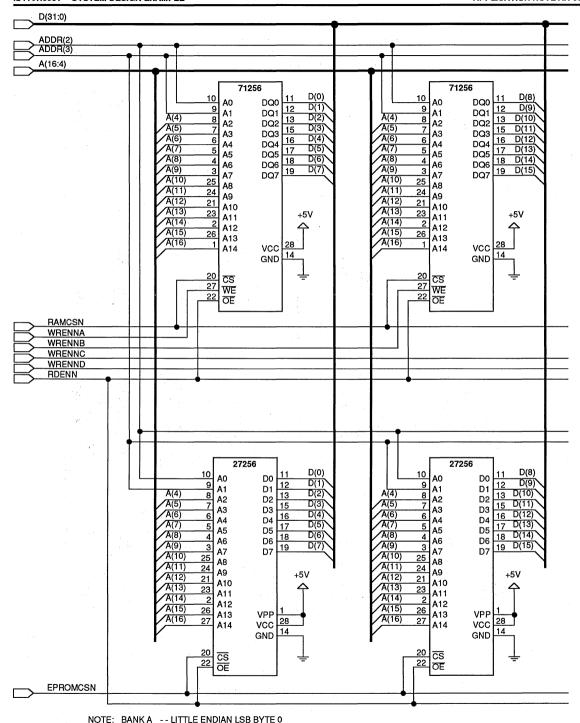

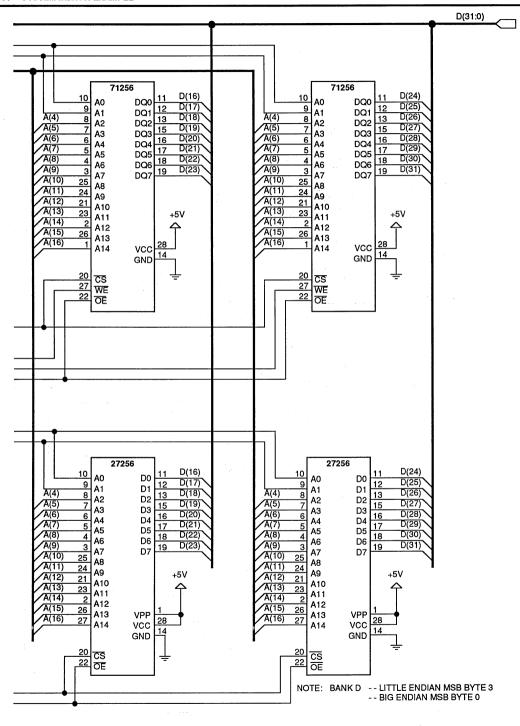

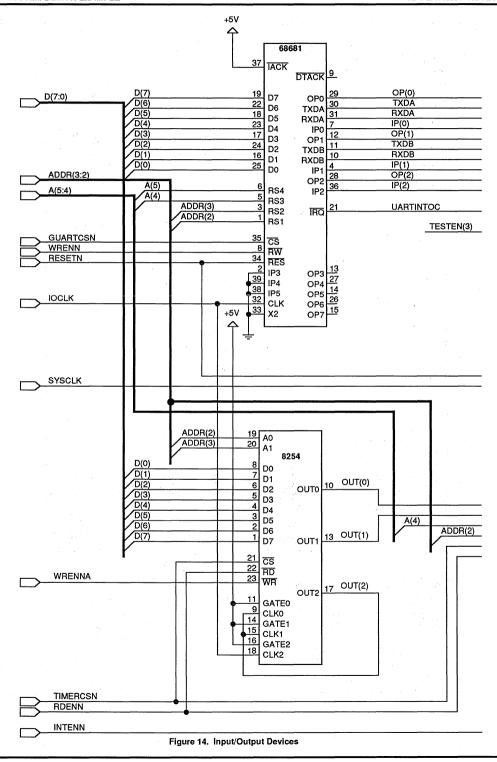

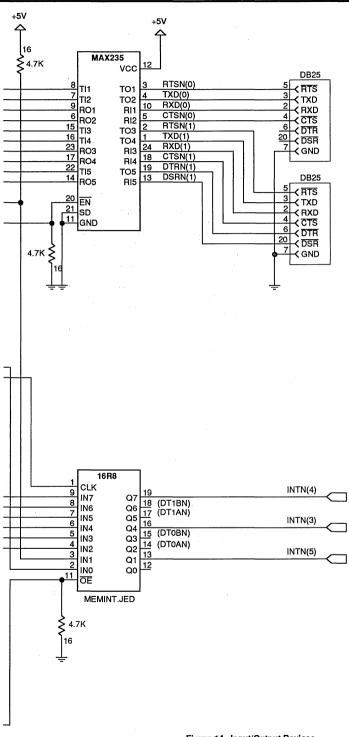

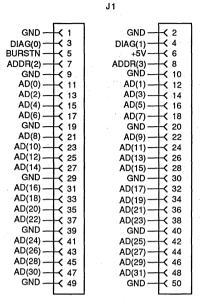

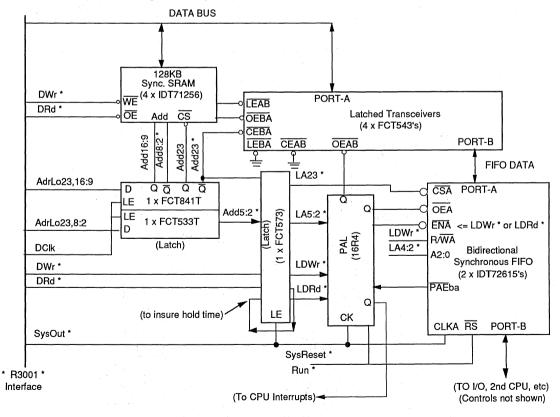

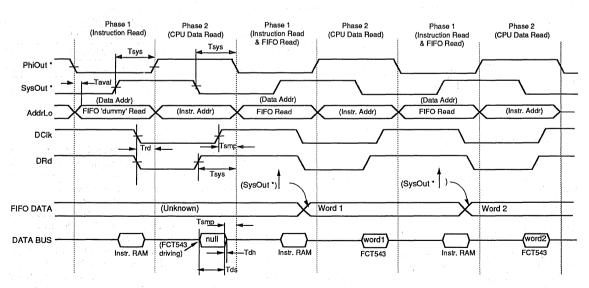

| AN-86                     | IDT79R3051™ System Design Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |           |

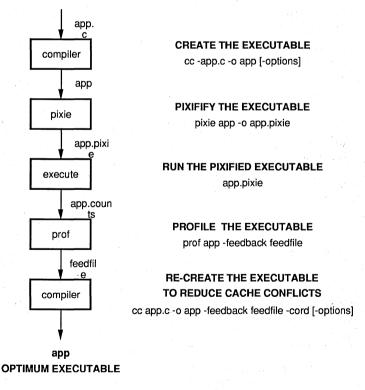

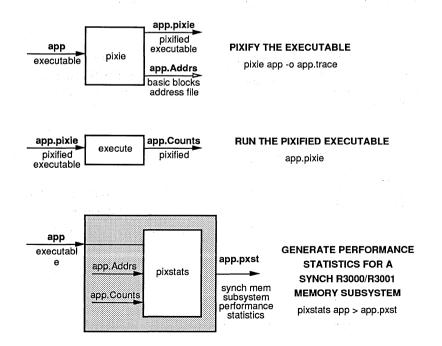

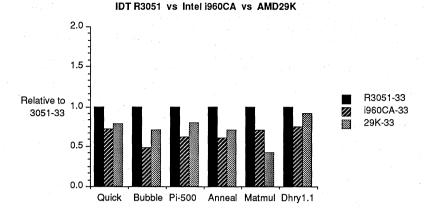

| AN-87                     | IDT79R3000/R3001 System Performance Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         |           |

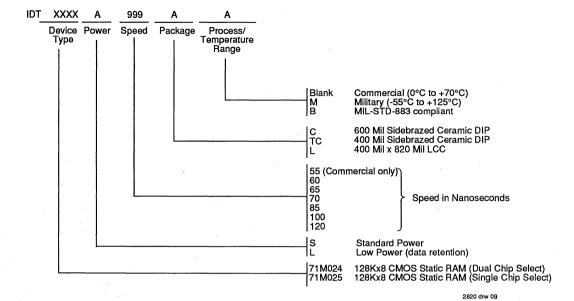

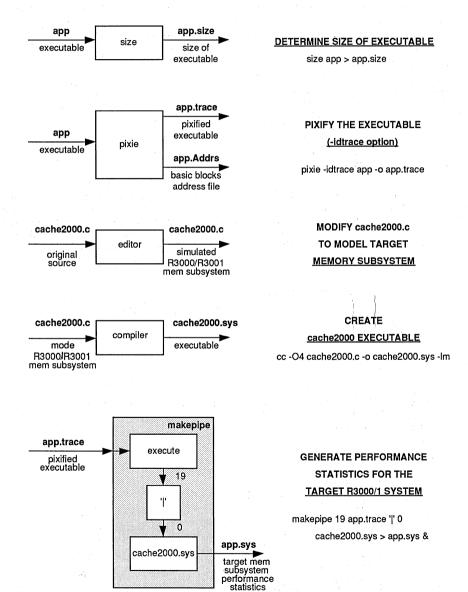

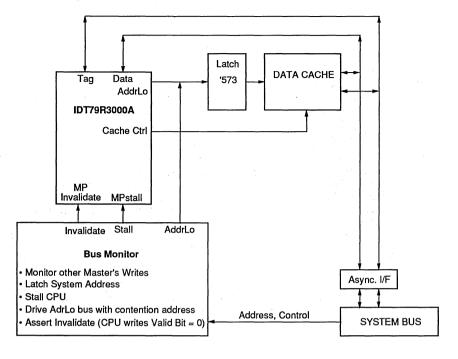

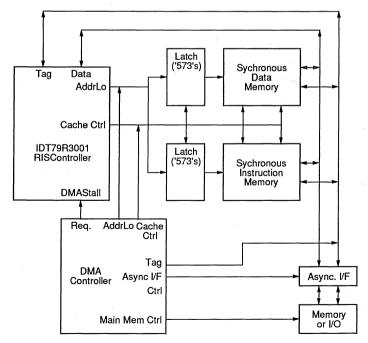

| AN-88                     | DMA Techniques with IDT's R3000/R3001 RISC CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         |           |