# RCA LSI Products — Applications

- Microprocessors Memories Peripheral Circuits

- Microboards Microsystems

# RCA LSI Products — Applications

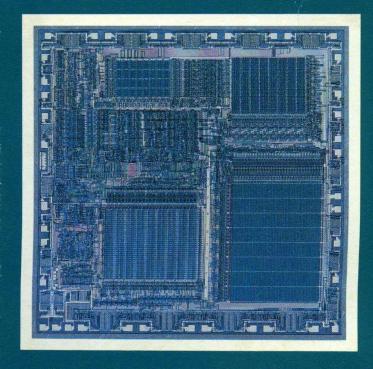

The RCA 1800 series of CMOS LSI products—microprocessors, memories, and peripheral support circuits—are used in many widely diverse applications covering a broad range of end markets. This series may be used, in some cases in combination with other industry-compatible peripherals, to provide the complete component requirements for a host of exciting and innovative systems, limited only by the ingenuity of the system designer. The 1800 series also encompasses a fully coordinated line of ready-to-use development and support systems (hardware and software) and Microboard computer modules for designers of microprocessor-based equipment.

RCA provides extensive literature support for the 1800-series products. Technical data bulletins contain detailed descriptive information on each type. Application notes provide helpful user information on most major types. This book is a collection of the current application notes on 1800-series products. Other technical literature used to support the 1800 series, including a comprehensive DATABOOK, system product descriptions, hardware and software user manuals, and product selection guides, are listed at the end of this book.

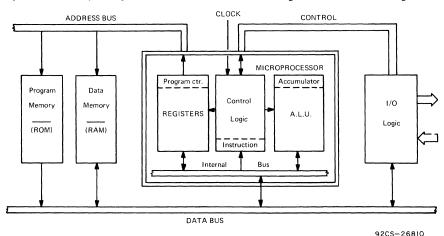

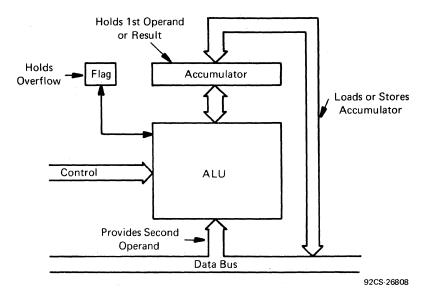

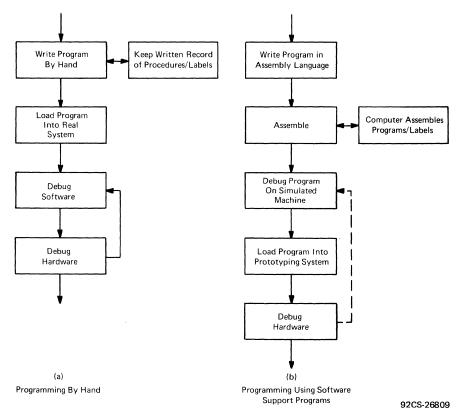

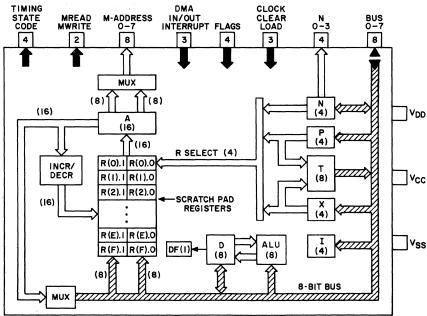

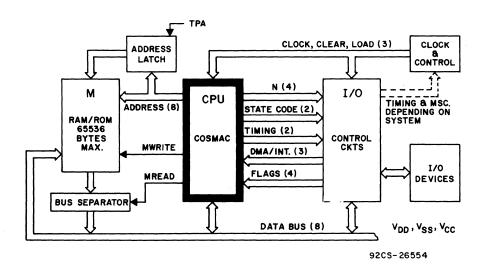

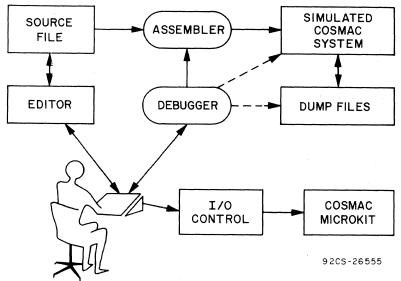

The application notes on 1800-series products describe specific hardware and software interface schemes of memory or peripheral components with an 1800-series central processing unit (CPU) and provide tutorial information on basic concepts, general device architecture and characteristics, and features and advantages of the 1800-series family. This information serves as a useful design guide to the system designer in determining the required hardware and software for his microcomputer-based design.

Information furnished by RCA is believed to be accurate and reliable. However, no responsibility is assumed by RCA for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of RCA.

When incorporating RCA Solid State Devices in equipment, it is recommended that the designer refer to "Operating Considerations for RCA Solid State Devices", Form No. 1CE-402, available on request from RCA Solid State Division, Box 3200, Somerville, N.J. 08876.

Copyright 1982 by RCA Corporation (All rights reserved under Pan-American Copyright Convention)

Trademark(s)®Registered Marca(s) Registrada(s)

Printed in USA/1-82

## **Table of Contents**

| Application Notes  ICAN-8315 COS/MOS Interfacing Simplified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Annliaat    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | age  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Application Notes  ICAN-6315 COS/MOS Interfacing Simplified  ICAN-6525 Guide to Better Handling and Operation of CMOS Integrated Circuits  ICAN-6526 Guide to Better Handling and Operation of CMOS Integrated Circuits  ICAN-6536 Use of CMOS ROM's CDP1831 and CDP1832 with the  RCA Microprocessor Evaluation Kit CDP188020  ICAN-6531 Use of CMOS RAM CDP1824 with Microprocessor Evaluation Kit CDP188020  ICAN-6532 Use of CMOS RAM CDP1824 with Microprocessor Evaluation Kit CDP188020  ICAN-6533 Use of CMOS RAM CDP1824 with Microprocessor Evaluation Kit CDP188020  ICAN-6539 Use of CMOS-SOS RAM CDP1822 with RCA Microprocessor Evaluation Kit CDP188020  ICAN-6539 Use of CMOS-SOS RAM CDP1822 with RCA Microprocessor Evaluation Kit CDP188020  ICAN-6565 Design of Clock Generators for Use with RCA COSMAC Microprocessor CDP1802  ICAN-6565 Design of Clock Generators for Use with RCA COSMAC Microprocessor CDP1802  ICAN-6595 Interfacing Analog and Digital Displays with CMOS Integrated Circuits  ICAN-6595 Interfacing Analog and Digital Displays with CMOS Integrated Circuits  ICAN-6596 Leve Some Some Some Some Some Some Some Som                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Applicat    | ion Note Classification Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| ICAN-6315 COS/MOS Interfacing Simplified ICAN-6316 ICAN-6316 An Introduction to Microprocessors and the RCA COSMAC COS/MOS Microprocessor.  21 ICAN-6326 Idade to Better Handling and Operation of CMOS Integrated Circuits 22 ICAN-6336 ILes of CMOS ROM's CDP1831 and CDP1832 with the RCA Microprocessor Evaluation Kit CDP185200. 28 ICAN-6337 ILes of CMOS RAM CDP1824 with Microprocessor Evaluation Kit CDP185200. 30 ICAN-6338 ILes of CMOS RAM CDP1824 with Microprocessor Evaluation Kit CDP185200. 30 ICAN-6338 ILes of CMOS RAM CDP1822 with RCA Microprocessor Evaluation Kit CDP185200. 30 ICAN-6358 ILes of CMOS RAM CDP1822 with RCA Microprocessor Evaluation Kit CDP185200. 31 ICAN-6362 Register-Based Output Function for RCA COSMAC Microprocessor Evaluation Kit CDP18520. 37 ICAN-6362 Register-Based Output Function for RCA COSMAC Microprocessor CDP1802. 42 ICAN-63631 Power-On Reset/Run Circuits for the RCA COSMAC Microprocessor CDP1802. 42 ICAN-6361 Interfacing COS/MOS with Other Logic Families Interfacing Analog and Digital Displays with CMOS Integrated Circuits 47 ICAN-6602 Interfacing COS/MOS with Other Logic Families ICAN-6615 ILes of the CDP1854 UART with RCA Microprocessor Evaluation Kit CDP185020 or EK/Assembler-Editor Design Kit CDP18502 ICAN-6635 ILes of CMOS ROM's CDP1833 and CDP1834 with the RCA Microprocessor Evaluation Kit CDP185020 or EK/Assembler-Editor Design Kit CDP185024 ICAN-6637 ILES OF INSERTION OF THE COMPTISE AND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | By Category | /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4    |

| ICAN-6315 COS/MOS Interfacing Simplified ICAN-6416 An Introduction to Microprocessors and the RCA COSMAC COS/MOS Microprocessor.  13 (ICAN-6526 Idude to Better Handling and Operation of CMOS Integrated Circuits 12 (ICAN-6536 ICAN-6537 Use of CMOS ROM's CDP1831 and CDP1832 with the RCA Microprocessor Evaluation Kit CDP185020.  28 (ICAN-6537 Use of CMOS RAM CDP1824 with Microprocessor Evaluation Kit CDP185020.  30 (ICAN-6537 Use of CMOS RAM CDP1824 with Microprocessor Evaluation Kit CDP185020.  31 (ICAN-6537 Use of CMOS RAM CDP1822 with RCA Microprocessor Evaluation Kit CDP185020.  32 (ICAN-6538 Use of CMOS RAM CDP1822 with RCA Microprocessor Evaluation Kit CDP185020.  33 (ICAN-6538 Use of CMOS RAM CDP1822 with RCA Microprocessor Evaluation Kit CDP185020.  34 (ICAN-6562 Register-Based Output Function for RCA COSMAC Microprocessor CDP1802.  35 (ICAN-6562 Interfacing COSMAC Microprocessor CDP1802.  36 (ICAN-65631 Power-On Reset/Run Circuits for the RCA COSMAC Microprocessor CDP1802.  37 (ICAN-6602 Interfacing COS/MOS with Other Logic Families  38 (ICAN-6511 Interfacing Analog and Digital Displays with CMOS Integrated Circuits  37 (ICAN-6602 Interfacing COS/MOS with Other Logic Families  38 (ICAN-6632 Use of the CDP1854 UART with RCA Microprocessor Evaluation Kit CDP185020 or EK/Assembler-Editor Design Kit CDP185024  38 (ICAN-6635 Use of the CDP1856 and CDP1857 Buffer/ Separators in CDP1802 Microprocessor Evaluation Kit CDP18020 or EK/Assembler-Editor Design Kit CDP185024  38 (ICAN-6637 Use of the CDP1856 and CDP1857 Buffer/ Separators in CDP1802 Microprocessor Systems  38 (ICAN-6630 ICAN-6637 Opt1802-Based Designs Using the 8253 Programmable Counter/Timer  39 (ICAN-6637 Opt1802-Based Designs Using the 8253 Programmable Counter/Timer  39 (ICAN-6637 Opt1802-Based Designs Using the 8253 Programmable Counter/Timer  30 (ICAN-6638) Inderstanding and Using the CDP1802 Microprocessor Applications  30 (ICAN-6636) Inderstanding and Using the CDP1802 Microprocessor Applications  30 (ICAN-6638) Inderstanding and Using the CDP1 | By Device T | ype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4    |

| ICAN-6416 An Introduction to Microprocessors and the RCA COSMAC COS/MOS Microprocessor ICAN-6527 ICAN-6538 Use of CMOS ROM's CDP1831 and CDP1832 with the RCA Microprocessor Evaluation Kit CDP185020.  ICAN-6538 Use of CMOS RAM CDP1824 with Microprocessor Evaluation Kit CDP185020.  ICAN-6538 Use of CMOS RAM CDP1824 with Microprocessor Evaluation Kit CDP185020.  33 ICAN-6538 Use of CMOS-SOS RAM CDP1822 with ROA Microprocessor Evaluation Kit CDP185020.  37 ICAN-6582 Register-Based Output Function for RCA COSMAC Microprocessor Evaluation Kit CDP185020.  37 ICAN-6562 Register-Based Output Function for RCA COSMAC Microprocessor Evaluation Kit CDP185020.  37 ICAN-6562 Register-Based Output Function for RCA COSMAC Microprocessor CDP1802.  42 ICAN-6581 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  45 ICAN-6682 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  47 ICAN-6682 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  47 ICAN-6683 Interfacing COS/MOS with Other Logic Families.  59 ICAN-6680 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  47 ICAN-6681 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  47 ICAN-6682 Interfacing COS/MOS with Other Logic Families.  59 ICAN-6681 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  47 ICAN-6682 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  47 ICAN-6683 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  47 ICAN-6684 Interfacing Analog and Digital Displays with the RCA Microprocessor Evaluation Kit CDP185020  47 ICAN-6685 Interfacing Analog and Digital Displays with the RCA Microprocessor Evaluation Kit CDP185020  47 ICAN-6687 Interfacing Analog and The EK/Assembler-Editor Design Kit CDP185024  50 Interfacing Analog and The Ek/Assembler-Editor Design Kit CDP185024  79 ICAN-6870 ICAN-6889 Interface Analog and The Ek/Assembler-Both The Analog Analog Analog Analog Analog Analog Analog Analog Analog Ana | Applica     | tion Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| ICAN-6416 An Introduction to Microprocessors and the RCA COSMAC COS/MOS Microprocessor ICAN-6527 ICAN-6538 Use of CMOS ROM's CDP1831 and CDP1832 with the RCA Microprocessor Evaluation Kit CDP185020.  ICAN-6538 Use of CMOS RAM CDP1824 with Microprocessor Evaluation Kit CDP185020.  ICAN-6538 Use of CMOS RAM CDP1824 with Microprocessor Evaluation Kit CDP185020.  33 ICAN-6538 Use of CMOS-SOS RAM CDP1822 with ROA Microprocessor Evaluation Kit CDP185020.  37 ICAN-6582 Register-Based Output Function for RCA COSMAC Microprocessor Evaluation Kit CDP185020.  37 ICAN-6562 Register-Based Output Function for RCA COSMAC Microprocessor Evaluation Kit CDP185020.  37 ICAN-6562 Register-Based Output Function for RCA COSMAC Microprocessor CDP1802.  42 ICAN-6581 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  45 ICAN-6682 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  47 ICAN-6682 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  47 ICAN-6683 Interfacing COS/MOS with Other Logic Families.  59 ICAN-6680 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  47 ICAN-6681 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  47 ICAN-6682 Interfacing COS/MOS with Other Logic Families.  59 ICAN-6681 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  47 ICAN-6682 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  47 ICAN-6683 Interfacing Analog and Digital Displays with CMOS Integrated Circuits.  47 ICAN-6684 Interfacing Analog and Digital Displays with the RCA Microprocessor Evaluation Kit CDP185020  47 ICAN-6685 Interfacing Analog and Digital Displays with the RCA Microprocessor Evaluation Kit CDP185020  47 ICAN-6687 Interfacing Analog and The EK/Assembler-Editor Design Kit CDP185024  50 Interfacing Analog and The Ek/Assembler-Editor Design Kit CDP185024  79 ICAN-6870 ICAN-6889 Interface Analog and The Ek/Assembler-Both The Analog Analog Analog Analog Analog Analog Analog Analog Analog Ana | ICAN 6215   | COS/MOS Interfering Circulified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| ICAN-6525 Guide to Better Handling and Operation of CMOS Integrated Circuits  121 (CAN-6537 Use of CMOS ROM's CDP1831 and CDP1832 with the RCA Microprocessor Evaluation Kit CDP18S020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| ICAN-6538 Use of CMOS ROM's CDP1831 and CDP1832 with the RCA Microprocessor Evaluation Kit CDP185020. 28 ICAN-6537 Use of CMOS RAM CDP1824 with Microprocessor Evaluation Kit CDP185020. 30 ICAN-6538 Use of CMOS-SOS RAM CDP1822 with RCA Microprocessor Evaluation Kit CDP185020. 33 ICAN-6539 Use of CMOS-SOS RAM CDP1822 with RCA Microprocessor Evaluation Kit CDP185020. 37 ICAN-6552 Register-Based Output Function for RCA COSMAC Microprocessor Evaluation Kit CDP185020. 37 ICAN-6552 Design of Ciock Generators for Use with RCA Microprocessor CDP1802. 42 ICAN-6581 Power-On Reset/Run Circuits for the RCA COSMAC Microprocessor CDP1802. 42 ICAN-6581 Interfacing Analog and Digital Displays with CMOS Interprated Circuits. 47 ICAN-6602 Interfacing COS/MOS with Other Logic Families ICAN-6617 Interfacing COS/MOS with Other Logic Families ICAN-6618 Interfacing Analog and Digital Displays with CMOS Interprated Circuits. 47 ICAN-6620 Interfacing COS/MOS with Other Logic Families ICAN-6619 Interfacing COS/MOS with Other Logic Families ICAN-6610 Interfacing COS/MOS with Other Logic Families ICAN-6620 Interfacing COS/MOS with Other Logic Families ICAN-6621 Use of the CDP1854 UART with RCA Microprocessor Evaluation Kit CDP185020 or EK/Assembler-Editor Design Kit CDP185020 Interfacing COS/MOS with CDP185020 Interface Society of COS/MOS With CDP185020 Interface Society Interfacing COS/MOS With CDP185020 Interface Society Inte |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

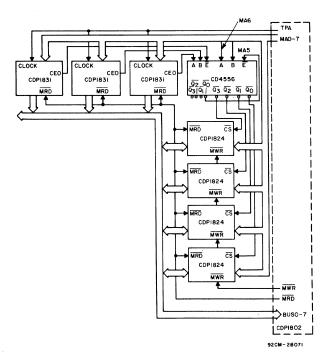

| ICAN-6537 ICAN-6539 IUse of CMOS RAM CDP1824 with Microprocessor Evaluation Kit CDP185020. 33 ICAN-6539 IUse of CMOS-SOS RAM CDP1822 with RCA Microprocessor Evaluation Kit CDP185020. 37 ICAN-6562 ICAN-6562 Register-Based Output Function for RCA COSMAC Microprocessor CDP1802. 42 Power-On Reset/Fun Circuits for the RCA CDP1802 COSMAC Microprocessor (ADR) Interfacing Analog and Digital Displays with CMOS Integrated Circuits. 47 ICAN-6602 ICAN-6602 ICAN-6602 ICAN-6603 ICAN-6603 ICAN-6604 ICAN-6605 ICAN-6606 ICAN-6607 ICAN-6608 ICAN-6608 ICAN-6608 ICAN-6608 ICAN-6609 ICAN-66 | ICAN-6536   | Use of CMOS ROM's CDP1831 and CDP1832 with the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

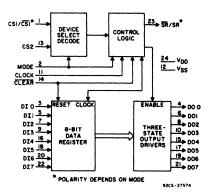

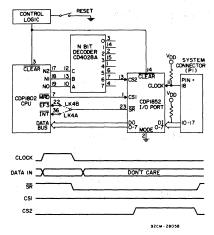

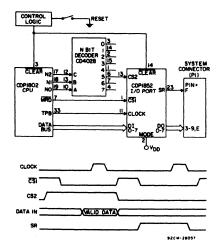

| ICAN-6538 Use of the CDP1852 8-Bit I/O Port with RCA Microprocessor Evaluation Kit CDP185020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ICAN 6527   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| ICAN-6539 ICAN-6530 ICAN-6540 ICAN-6550 ICAN-6550 ICAN-6550 ICAN-6550 ICAN-6550 ICAN-6550 ICAN-6550 ICAN-6551 ICAN-6551 ICAN-6551 ICAN-6561 ICAN-6561 ICAN-6561 ICAN-6562 ICAN-6562 ICAN-6562 ICAN-6562 ICAN-6562 ICAN-6562 ICAN-6602 ICAN-6602 ICAN-6602 ICAN-6603 ICAN-6603 ICAN-6604 ICAN-6604 ICAN-6605 ICAN-6605 ICAN-6605 ICAN-6605 ICAN-6606 ICAN-6606 ICAN-6606 ICAN-6606 ICAN-6607 ICAN-6608 ICAN-6608 ICAN-6608 ICAN-6608 ICAN-6608 ICAN-6608 ICAN-6609 ICAN-6 |             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| ICAN-6562 Register-Based Output Function for RCA COSMAC Microprocessors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| ICAN-6565 Design of Clock Generators for Use with RCA COSMAC Microprocessor CDP1802 . 42 ICAN-6581 Power-On Reset/Run Circuits for the RCA CDP1802 COSMAC Microprocessor . 45 ICAN-6602 Interfacing Analog and Digital Displays with CMOS Integrated Circuits . 47 ICAN-6602 Interfacing COS/MOS with Other Logic Families . 59 Interfacing COS/MOS with Other Logic Families . 59 ICAN-6613 Use of the CDP1854 UART with RCA Microprocessor Evaluation Kit CDP18S020 or EK/Assembler-Editor Design Kit CDP183024 . 74 ICAN-6632 Use of CMOS ROM's CDP1833 and CDP1834 with the RCA Microprocessor Evaluation Kit CDP18S020 and the EK/Assembler-Editor Design Kit CDP185024 . 79 ICAN-6632 Use of the CDP1865 and CDP1867 Buffer/ Separators in CDP1802 Microprocessor Systems . 82 ICAN-6637 Use of the CDP1865 and CDP1867 Buffer/ Separators in CDP1802 Microprocessor Systems . 82 ICAN-6637 Use of the CDP1865 and CDP1865 Buffer/ Separators in CDP1802 Microprocessor Systems . 82 ICAN-6647 Optimizing Hardware/Software Trade-Offs in RCA CDP1802 Microprocessor Applications . 97 ICAN-6834 Microprocessor Control for Color-TV Receivers . 107 ICAN-6840 Is-Bit Operations in the CDP1802 Microprocessor . 117 ICAN-6841 Programming 2732 PROM's with the CDP18040 PROM Programmer . 122 ICAN-6801 Using Slower Memories with the VIS Display System . 125 ICAN-6802 Using Slower Memories with the VIS Display System . 125 ICAN-6803 A Methodology for Programming COSMAC 1802 Applications Using Higher-Level Languages . 137 ICAN-6948 Parallel Clocking of Sequential CMOS Devices . 140 Interfacing PLM Code to CDOS System Functions . 149 Interfacing PLM Code to CDOS System Functions . 149 ICAN-6948 Designing Minimum/Nonvolatile Memory Systems with CMOS Static RAM's . 159 ICAN-6949 Parallel Clocking of Sequential CMOS Devices . 154 ICAN-6949 New CDP1802 Serial Princitons CDP1804 Buffer System . 126 ICAN-6940 New CDP1805 Serial Princitons CDP1806 Based Systems . 126 ICAN-6951 A Siave CDP1805 Serial Princits System Performance and Lower Chip Count . 202 ICAN-6961 New CDP1805 Seria |             | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| ICAN-6581 Power-On Reset/Run Circuits for the RCA CDP1802 COSMAC Microprocessor  (CAN-6595 Interfacing Analog and Digital Displays with CMOS Integrated Circuits  47 Interfacing COS/MOS with Other Logic Families  59 ICAN-6611 Keyboard Scan Routine for Use with COSMAC Microterminal CDP18S021  71 ICAN-6622 Use of the CDP1854 UART with RCA Microprocessor Evaluation Kit CDP18S020 or  EK/Assembler-Editor Design Kit CDP18S024  74 ICAN-6635 Use of CMOS ROM's CDP1833 and CDP18S024  75 ICAN-6657 Use of CMOS ROM's CDP1833 and CDP1834 with the RCA Microprocessor Evaluation Kit CDP18S020 and the EK/Assembler-Editor Design Kit CDP18S024  79 ICAN-6657 Use of the CDP1856 and CDP1857 Buffer/ Separators in CDP1802 Microprocessor Systems  82 ICAN-6667 Optimizing Hardware/Software Trade-Offs in RCA CDP1802 Microprocessor Systems  83 ICAN-6693 CDP1802-Based Designs Using the 8253 Programmable Counter/Timer  94 ICAN-6704 Optimizing Hardware/Software Trade-Offs in RCA CDP1802 Microprocessor Applications  97 ICAN-6842 16-Bit Operations in the CDP1802 Microprocessor  107 ICAN-6843 Microprocessor Control for Color-TV Receivers  107 ICAN-6844 Is-Bit Operations in the CDP1802 Microprocessor  117 ICAN-6849 Using Slower Memories with the VIS Display System  126 ICAN-6889 Using Slower Memories with the VIS Display System  127 ICAN-6898 Understanding and Using the CDP18042 PROM Programmer  128 Interfacing PLM Code to CDOS System Functions  129 Understanding and Using the CDP18042 EPROM  120 Interfacing PLM Code to CDOS System Functions  120 Interfacing PLM Code to CDOS System Functions  120 Understanding and Using the CDP18042 PROM Microprocessor Systems  126 ICAN-6934 Designing Minimum/Nonvolatile Memory Systems with CMOS Static RAM's  129 Understanding and Using the CDP1805 Miltiply/Divide Unit  120 ICAN-6937 Designing Minimum/Nonvolatile Memory Systems with CMOS Static RAM's  129 Interfacing PLM Code to CDOS System Functions  120 Interfacing PLM Code to CDOS System Functions  120 Interfacing PLM Code to CDOS System Functions  120 Interfaci |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| ICAN-6595 Interfacing Analog and Digital Displays with CMOS Integrated Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| ICAN-6611 Keyboard Scan Routine for Use with COSMAC Microterminal CDP18S021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| ICAN-6612 Use of the CDP1854 UART with RCA Microprocessor Evaluation Kit CDP185020 or EK/Assembler-Editor Design Kit CDP185024.  (CAN-6635 Use of CMCS ROM's CDP1833 and CDP1833 with the RCA Microprocessor Evaluation Kit CDP185024.  (CAN-6637 Use of CMCS ROM's CDP1835 and CDP1833 with the RCA Microprocessor Evaluation Kit CDP185024 and the EK/Assembler-Editor Design Kit CDP185024.  (CAN-6657 Use of the CDP1856 and CDP1857 Buffer/ Separators in CDP1802 Microprocessor Systems.  (CAN-6670 Use of the CDP1856 and CDP1857 Buffer/ Separators in CDP1802 Microprocessor Systems.  (CAN-6670 CDP1802-Based Designs Using the 8253 Programmable Counter/Timer.  (CAN-6840 Microprocessor Control for Color-TV Receivers.  (CAN-6841 In-Bit Operations in the CDP1802 Microprocessor.  (CAN-6842 In-Bit Operations in the CDP1802 Microprocessor.  (CAN-6847 Programming 2732 PROM's with the CDP1880480 PROM Programmer.  (CAN-6848 Simplified Design of Astable RC Oscillators Using the CD4060B or Two CMOS Inverters.  (CAN-6889 Using Slower Memories with the VIS Display System.  (CAN-6890 Understanding and Using the CD41802 Applications Using Higher-Level Languages.  (CAN-6925 Understanding and Using the CD71804 EPROM.  (CAN-6934 Cassette Tape I/O for COSMAC 1802 Applications Using Higher-Level Languages.  (CAN-6935 Understanding and Using the CD71804 EPROM.  (CAN-6936 An Introduction to the Video Interface System With CMOS Static RAM's.  (CAN-6935 Understanding and Using the CD71805 Processors Pasaed Set Designing Minimum/Nonvolatile Memory Systems with CMOS Static RAM's.  (CAN-6935 Understanding and Using the CD71805 Multiply/Divide Unit .  (CAN-6936 New CMOS CDP1800-Series Processors Enhance System Performance and Lower Chip Count.  (CAN-6936 Understanding and Using the CD71805 Multiply/Divide Unit .  (CAN-6937 Understanding and Using the CD71805 Multiply/Divide Unit .  (CAN-6936 Understanding and Using the CD71805 Multiply/Divide Unit .  (CAN-6937 New CMOS CDP1800-Series Processors Enhance System Performance.  (CAN-7038 Microprocessor-Based T |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| ICAN-6632 Use of the CDP1854 UART with RCA Microprocessor Evaluation Kit CDP18S020 or EK/Assembler-Editor Design Kit CDP18S024.  ICAN-6635 Use of CMOS ROM's CDP1833 and CDP1834 with the RCA Microprocessor Evaluation Kit CDP18S020 and the EK/Assembler-Editor Design Kit CDP18S024.  79 ICAN-6657 Use of the CDP1856 and CDP1857 Buffer/ Separators in CDP1802 Microprocessor Systems.  82 ICAN-6678 Software Control of Microprocessor-Based Realtime Clock.  85 ICAN-6680 CDP1802-Based Designs Using the 8253 Programmable Counter/Timer.  94 ICAN-6684 Optimizing Hardware/Software Trade-Offs in RCA CDP1802 Microprocessor Applications.  97 ICAN-6844 Microprocessor Control for Color-TV Receivers.  107 ICAN-6847 Programming 2732 PROM's with the CDP185480 PROM Programmer.  117 ICAN-6889 Using Slower Memories with the VIS Display System.  127 ICAN-6989 Using Slower Memories with the VIS Display System.  127 ICAN-6918 A Methodology for Programming COSMAC 1802 Applications Using Higher-Level Languages.  137 ICAN-6928 Interfacing PLM Code to CDOS System Functions.  149 Interfacing PLM Code to CDOS System Functions.  140 Interfacing PLM Code to CDOS System Functions.  140 Interfacing PLM Code to CDOS System Functions.  140 Interfacing PLM Code to CDOS System Functions.  141 ICAN-6934 Cassette Tape I/O for COSMAC Microprocessor Systems with CMOS Static RAM's  140 Interfacing PLM Code to CDOS System Functions.  141 ICAN-6948 Parallel Clocking of Sequential CMOS Devices.  142 Interfacing PLM Code to CDOS System Functions.  143 Interduction to the Video Interface System (VIS) Devices—CDP1869 and CDP1870.  144 ICAN-6953 An Introduction to the Video Interface System With CMOS Static RAM's  145 ICAN-6964 Designing Minimum/Novolatile Memory Systems with CMOS Static RAM's  146 ICAN-6967 Understanding and Using the CDP1855 Multiply/Divide Unit  147 ICAN-6967 Understanding and Using the CDP1855 Multiply/Divide Unit  148 ICAN-6971 New CMOS CDP1800-Series Processors Reduce Chip Count  149 ICAN-6971 New CMOS CDP1800-Series Processors Reduce Chip Cou |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |