SEMICONDUCTORS

AMS-501

#### INTEGRATED AND DISCRETE

# **SEMICONDUCTORS**

#### Applications for

- **■** EDP Peripherals

- Industrial Control

- **■** Motor & Power Drive

- Office Automation

- Mass Storage

- Automotive

- Consumer

- Displays

- Power Management

### Allegro MicroSystems, Inc.

Formerly Sprague Semiconductor Group

115 Northeast Cutoff, Box 15036 Worcester, MA 01615 (508) 853-5000

# TABLE OF CONTENTS

| 1. | GENERAL INFORMATION & PRODUCT INDEX                           |

|----|---------------------------------------------------------------|

|    | Allegro MicroSystems, Inc 1-1                                 |

|    | Definition of Terms 1-3                                       |

|    | Allegro Package Designators1-5                                |

|    | Allegro Part Numbering Systems1-6                             |

|    | Ordering Information 1-8                                      |

|    | Technical Assistance                                          |

|    | Product Index (ICs and Transistor Arrays) 1-9                 |

|    | See Also:                                                     |

|    | Discrete Semiconductors Index and Cross Reference 7-2         |

|    | Sales Offices and RepresentativesBack of Book                 |

|    |                                                               |

| 2. | PRODUCT SELECTION GUIDES                                      |

|    | Peripheral Power and Display Drivers 2-1                      |

|    | High-Voltage (≥80 V) Peripheral Power and Display Drivers 2-3 |

|    | BiMOS Intelligent Power Interface Drivers 2-4                 |

|    | Motor Drivers 2-5                                             |

|    | Hall-Effect Sensors                                           |

|    | Devices for Mass Storage Applications 2-7                     |

|    | Devices for Printer Applications2-7                           |

|    | Automotive, Signal Processing, and Consumer ICs 2-8           |

|    | Integrated Circuits Cross-Reference 2-10                      |

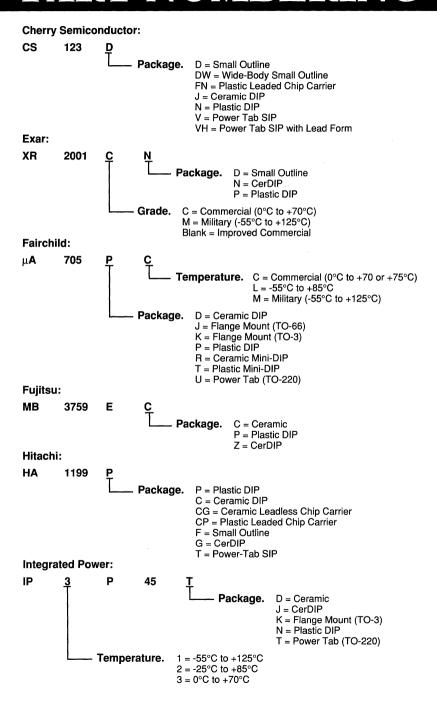

|    | Competitive Integrated Circuits Part-Numbering Systems 2-16   |

|    | See Also:                                                     |

|    | Quick Guide to Allegro Discrete Devices                       |

|    | Discrete Semiconductors Index and Cross Reference 7-2         |

|    | Discrete and Integrated Circuit                               |

|    | Semiconductor Chips Brochure CN-193                           |

| 3. | TECHNICAL DATA & APPLICATION NOTES                            |

|    | for Peripheral Power and Display Driver ICs                   |

|    | in Numerical Order Beginning at 3-1                           |

|    | Applications Information:                                     |

|    | Power ICs for Motor-Drive Applications                        |

|    | Integrated Circuits for Current-Sourcing Applications 3-229   |

|    | Expanding the Frontiers of IC Interface                       |

|    | for Electronic Displays 3-239                                 |

|    | Trends in IC Interface for Electronic Displays 3-245          |

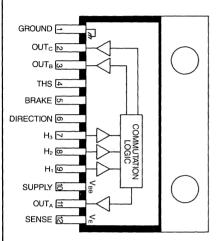

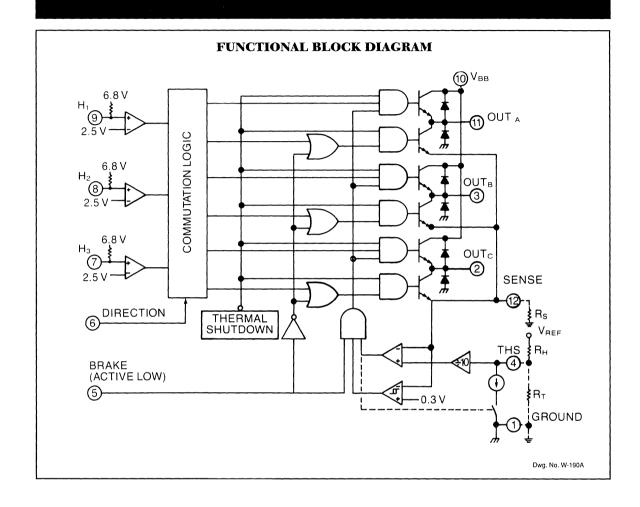

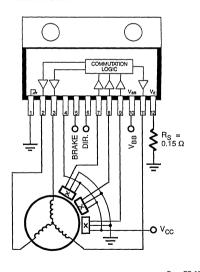

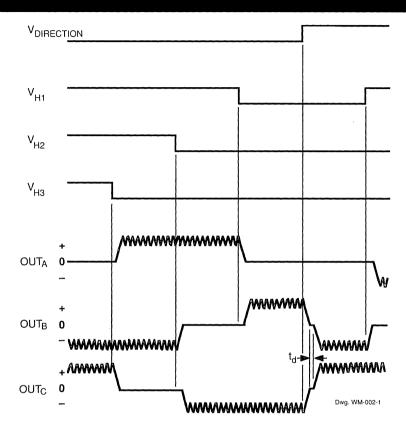

|    | 2936 3-Phase Brushless DC Motor Controller/Driver 3-251       |

|    | Series 5800 BiMOS II Power Drivers 3-255                      |

|    | See Also:                                                     |

|    | Reliability ReportsSection 8                                  |

|    |                                                               |

### TABLE OF CONTENTS

| 4.  | TECHNICAL DATA & APPLICATION NOTES for Hall-Effect Sensor ICs       |

|-----|---------------------------------------------------------------------|

|     | in Numerical Order Beginning at 4-                                  |

|     | Applications Information:                                           |

|     | Hall Effect Applications Guide 4-74                                 |

|     | The Hall Effect Sensor 4-10                                         |

| 5.  | TECHNICAL DATA & APPLICATION NOTES for Mass Storage Application ICs |

|     | in Numerical OrderBeginning at 5-                                   |

| 6.  | TECHNICAL DATA & APPLICATION NOTES                                  |

|     | for Automotive, Signal-Processing, and Consumer ICs                 |

|     | in Numerical OrderBeginning at 6-                                   |

| 7.  | TECHNICAL DATA                                                      |

|     | for Discrete Transistors, Diodes, and Arrays                        |

|     | Quick Guide to Discrete Devices                                     |

|     | Discrete Semiconductors Index and Cross Reference 7-2               |

|     | Discrete Devices Ratings:                                           |

|     | NPN Bipolar Transistors 7-14                                        |

|     | PNP Bipolar Transistors 7-10                                        |

|     | N-Channel Junction Field-Effect Transistors                         |

|     | P-Channel Junction Field-Effect Transistors                         |

|     | General-Purpose and Schottky Diodes                                 |

|     | Zener Diodes                                                        |

|     | Transistor and Diode Arrays                                         |

|     | See Also:                                                           |

|     | High-Current Darlington Transistor Arrays Section                   |

|     | Discrete and Integrated Circuit                                     |

|     | Semiconductor Chips Brochure CN-19                                  |

| 8.  | QUALITY & RELIABILITY INFORMATION                                   |

|     | Reliability                                                         |

|     | PACE Primer                                                         |

|     | Reliability Reports:                                                |

|     | Series 2000 and 2800 Darlington Drivers                             |

| - / | Series 5800 BiMOS Drivers                                           |

|     | Series 6100 High-Voltage Display Drivers                            |

|     | SOT-23 Transistors                                                  |

|     |                                                                     |

### TABLE OF CONTENTS

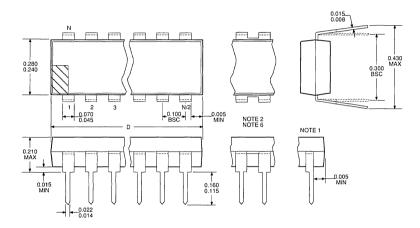

| υ. | PACKAGE INFORMATION                                                 |              |

|----|---------------------------------------------------------------------|--------------|

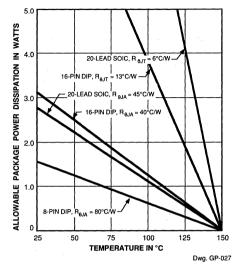

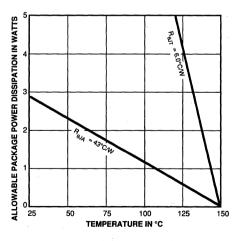

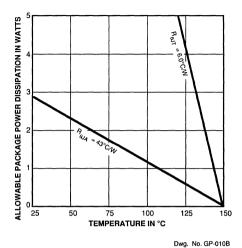

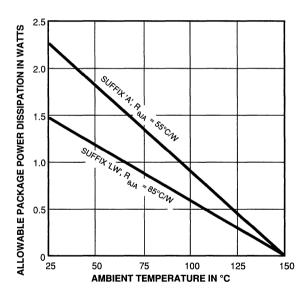

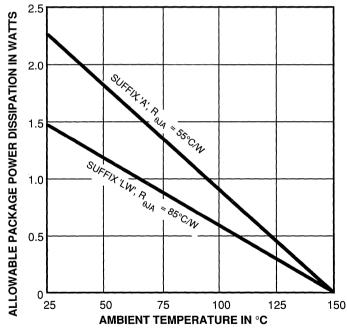

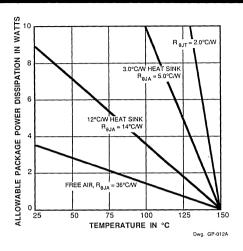

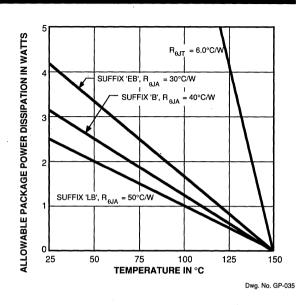

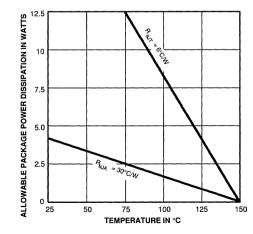

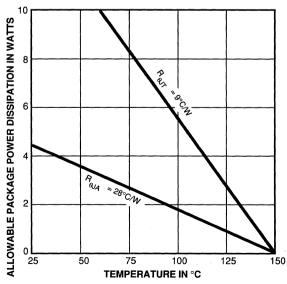

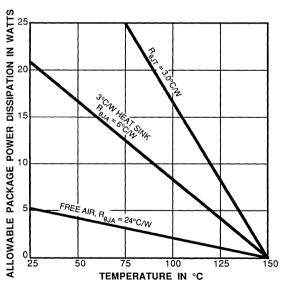

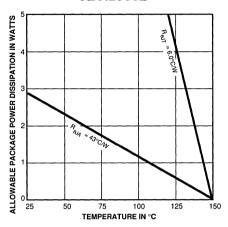

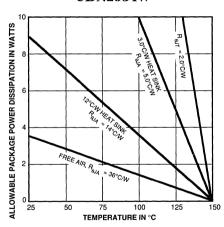

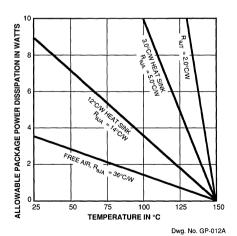

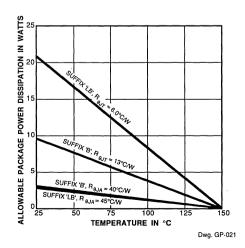

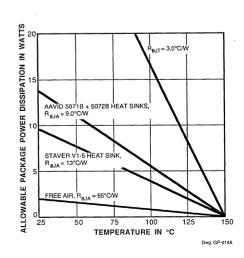

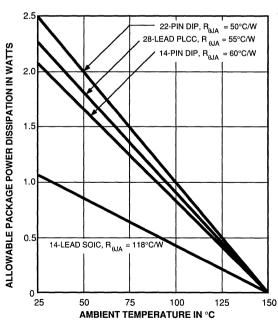

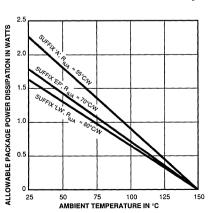

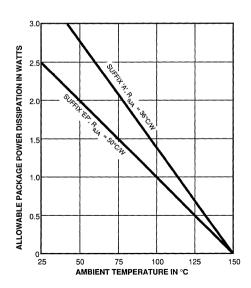

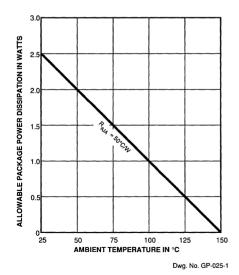

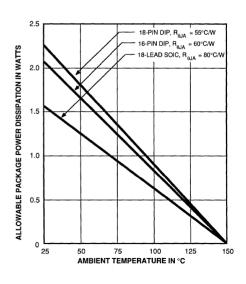

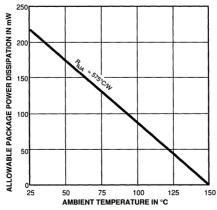

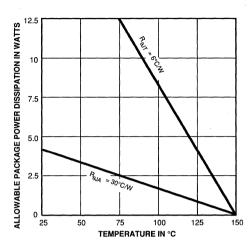

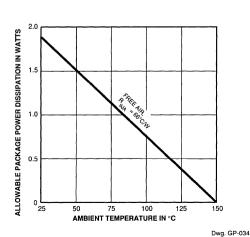

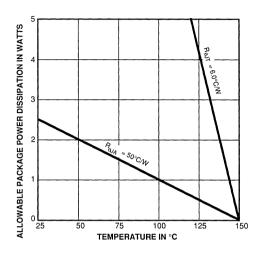

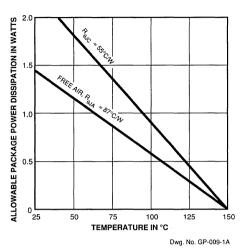

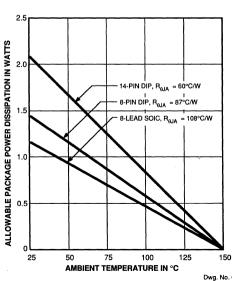

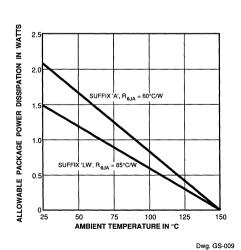

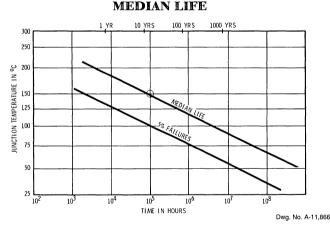

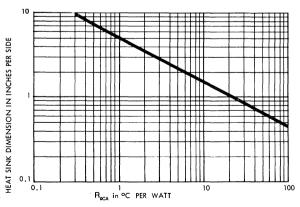

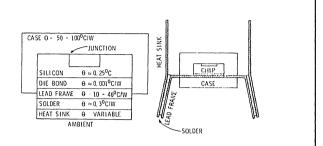

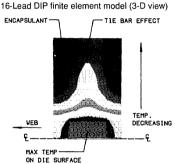

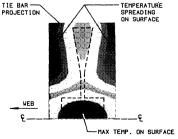

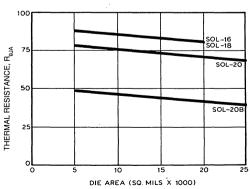

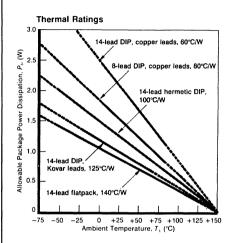

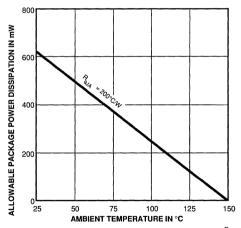

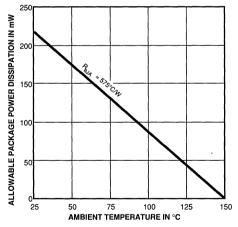

|    | Package Thermal Characteristics                                     | 9-1          |

|    | Thermal Design for Plastic Integrated Circuits                      | 9-3          |

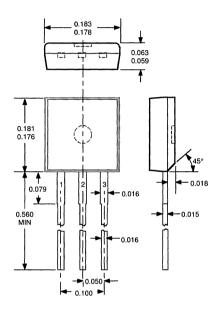

|    | High-Performance Power Package for Power-Integrated Circuit Devices | 9-7          |

|    | Applications Information:                                           |              |

|    | Electrostatic Protection for Semiconductor Products                 | 9-19         |

|    | Operating and Handling Practices for MOS Integrated Circuits        | 9-21         |

|    | Mounting Power Tab Devices                                          | <b>9-2</b> 1 |

|    | Surface-Mount Integrated Circuits                                   | 9-22         |

|    | Computing IC Temperature Rise                                       | 9-25         |

|    | Thermal Resistance — A Reliability Consideration                    | 9-30         |

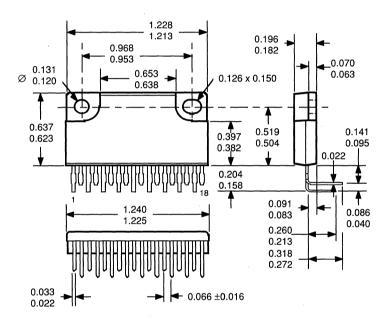

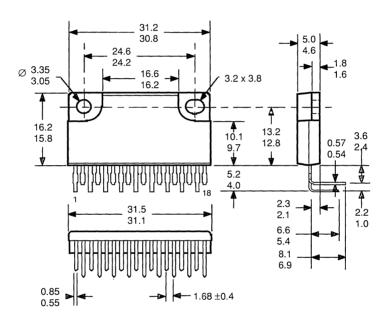

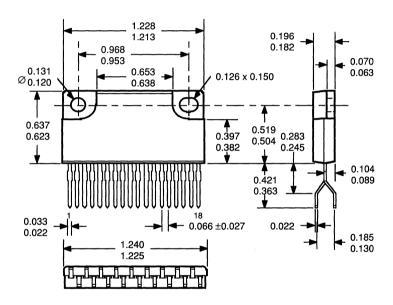

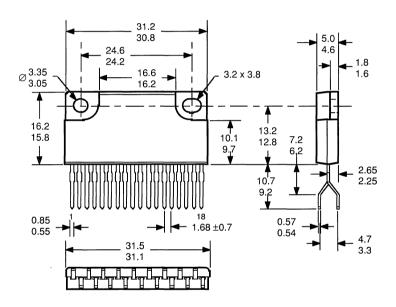

|    | Package Outline Drawings                                            | 9-39         |

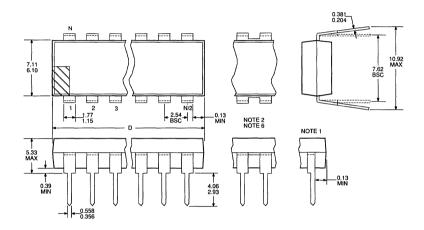

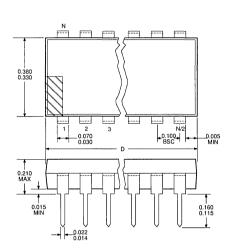

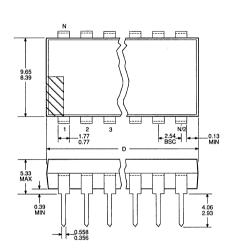

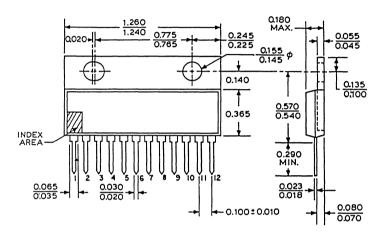

|    | A, B, & M Plastic DIPs                                              | 9-39         |

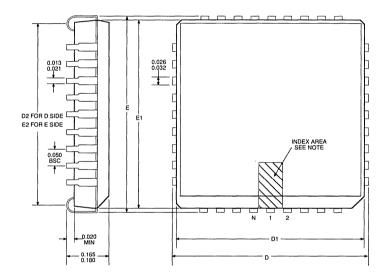

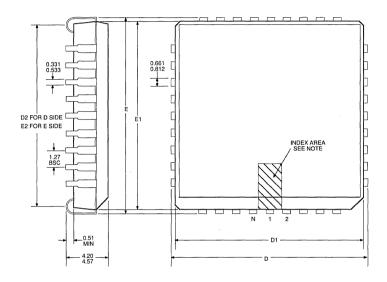

|    | EA, EB, & EP Square Plastic Leaded Chip Carriers                    | 9-45         |

|    | EQ Rectangular Plastic Leaded Chip Carrier                          | 9-47         |

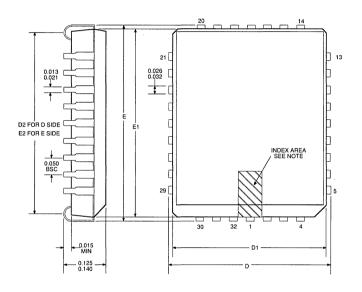

|    | JT Thin Quad Flatpack                                               | 9-49         |

|    | K Plastic SIP                                                       | 9-51         |

|    | KA Plastic SIP                                                      | 9-52         |

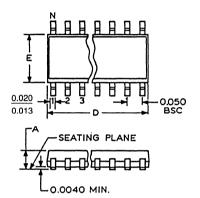

|    | L Plastic SOICs                                                     | 9-53         |

|    | LB & LW Wide-Body Plastic SOICs                                     | 9-55         |

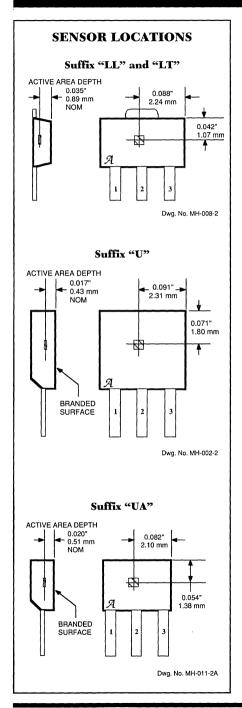

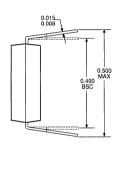

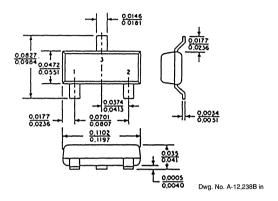

|    | LL Long-Leaded Plastic SOT                                          | 9-57         |

|    | LR Plastic Small-Outline Transistor                                 | 9-68         |

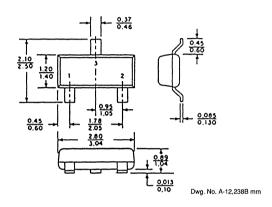

|    | LT Plastic SOT                                                      | 9-58         |

|    | U Plastic SIP                                                       | 9-59         |

|    | UA Plastic SIP                                                      | 9-60         |

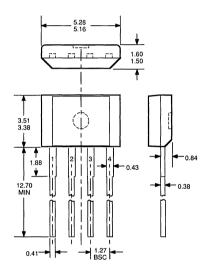

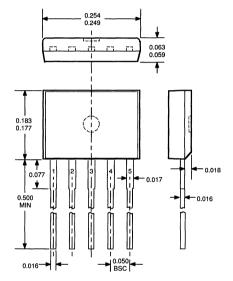

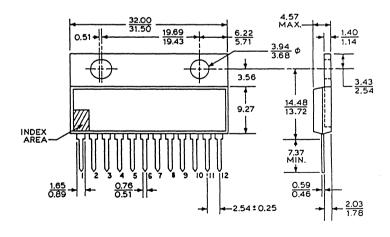

|    | W Plastic Power-Tab SIP                                             | 9-61         |

|    | WH Plastic Power-Tab SIP for Horizontal Mounting                    | 9-62         |

|    | WV Plastic Power-Tab SIP for Vertical Mounting                      | 9-62         |

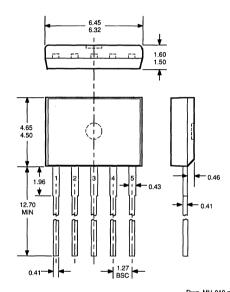

|    | Z Plastic Power-Tab SIP                                             | 9-66         |

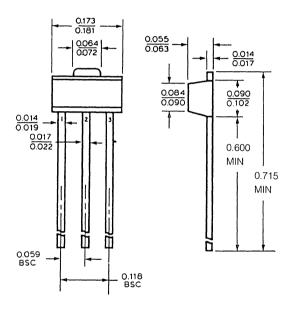

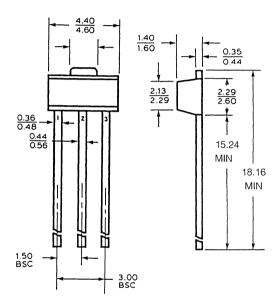

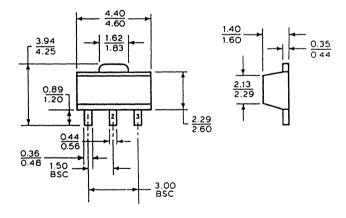

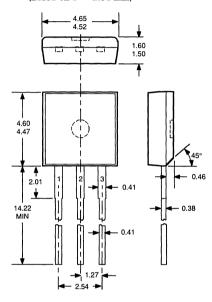

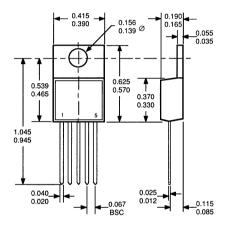

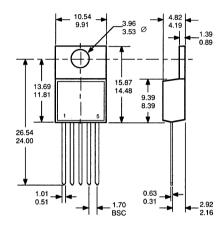

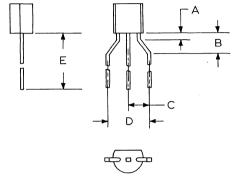

|    | Plastic Transistor                                                  | 9-67         |

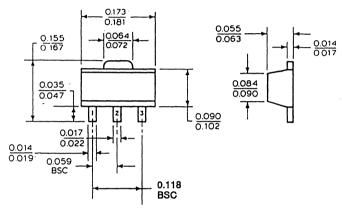

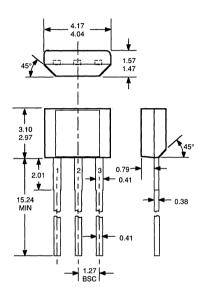

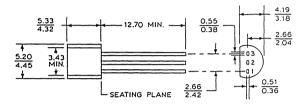

|    | Plastic Small-Outline Transistor                                    | 9-68         |

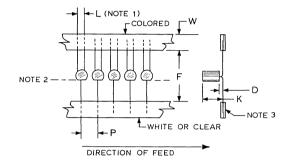

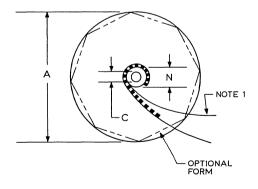

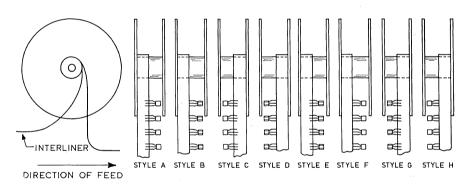

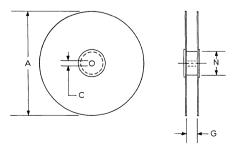

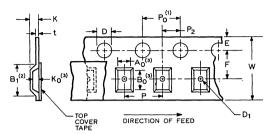

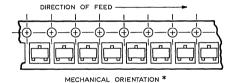

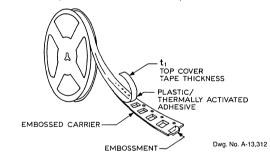

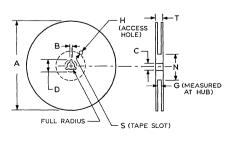

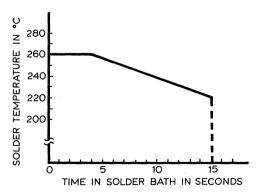

|    | Tape and Reel Information for Discrete Devices                      | 9-69         |

| SA | LES OFFICES & REPRESENTATIVES                                       |              |

|    | World-Wide Back of                                                  | f Book       |

### **GENERAL INFORMATION & PRODUCT INDEX**

AND THE PROPERTY OF THE PROPER

PAPERPETE PER PANEO E AS DECUMENTARIO

HAMILION OF STREET

MASS STORAGE APPEARATION IC

AUTOMOTIVE, SIGNAL-PROCESSING. & CONSUMERIES

DISCRETE TRANSISTORS, DIODES, & ARRAYS

QUALITY & RELIABILITY INFORMATION

PACKAGE INFORMATION

#### SECTION 1. GENERAL INFORMATION & PRODUCT INDEX

| Allegro MicroSystems, Inc.                        | 1-1          |

|---------------------------------------------------|--------------|

| Definition of Terms                               | 1-3          |

| Allegro Package Designators                       | 1-5          |

| Allegro Part Numbering Systems                    | 1-6          |

| Ordering Information                              | 1-8          |

| Technical Assistance                              | 1-8          |

| Product Index (ICs and Transistor Arrays)         | 1-9          |

| See Also:                                         |              |

| Discrete Semiconductors Index and Cross Reference | 7-2          |

| Sales Offices and Representatives                 | Back of Book |

## GENERAL INFORMATION

### ALLEGRO MICROSYSTEMS, INC.

Allegro MicroSystems, Inc. specializes in the design, manufacture, and marketing of advanced mixed-signal (analog + digital) integrated circuits as well as a line of discrete transistors and diodes. Allegro, formerly the Sprague Semiconductor Group, combines over 25 years of semiconductor experience, over a decade of extensive merged-technologies experience, and worldwide resources in design and applications engineering, process technology, packaging, quality control, manufacturing, and testing.

Allegro is a leading supplier of mixed-signal solutions and emphasizes system-level ICs for original equipment manufacturers that primarily serve the computer peripherals, automotive, consumer, and industrial markets. Allegro's strengths center on an excellent track record in product quality and innovation, and a diversified base of major OEM customers. The company's reputation for quality spans both product design and manufacturing. This reputation is evident in preferred vendor/ship-to-stock programs. Allegro has received quality awards from leading manufacturers worldwide, and is the only US IC manufacturer to have received IECQ manufacturer's approval.

Headquartered in Worcester, Massachusetts, Allegro currently operates two wafer-fabrication plants in Worcester and Willow Grove, Pennsylvania, as well as assembly/test operations in the Philippines.

Allegro's product expertise in power ICs, signal processing ICs, and sensor ICs—believed to be unique in the industry—is supported by strong capabilities in bipolar, CMOS, and DMOS process technologies. Allegro can and does combine any two or all three of its product disciplines (and/or process technologies) in a single monolithic chip to deliver powerful system-level solutions.

### GENERAL INFORMATION ALLEGRO MICROSYSTEMS, INC.

Within the worldwide semiconductor market, Allegro has strategically positioned itself in the analog segment. Allegro primarily serves the analog IC industry through the development, manufacture, and marketing of a wide variety of complex products. The company emphasizes application-specific, market-driven products with high technology content. These include bipolar, CMOS, and DMOS technologies, as well as merged technologies such as BiCMOS (bipolar + CMOS), BCD (bipolar + CMOS + DMOS), and DABIC (digital + analog + BiCMOS).

Analog ICs can generally be separated into three classifications: sensor, signal processing, and power ICs. Sensors are analog ICs which respond to physical phenomena and provide inputs to an electronic system. Signal processing ICs represent a broad category of analog ICs which accept, generate, or process an analog signal. Power ICs are those products which act as the interface from an electronic system back to the physical world. These products typically operate at voltages and currents well in excess of those applied to other parts of the electronic system due to their requirement to drive motors, displays, solenoids, relays, lamps, and other devices.

At Allegro, original designs are emphasized, rather than second source products, in order to command a higher value in the market-place. Many of these original designs have ultimately become industry standard products, such as the company's popular Hall-effect switches and power drivers.

Customers expect suppliers to add tangible value at a system level because they need to maximize performance and speed time to market. Applications, design, and technology consultation provided by IC suppliers, therefore, become crucial, as does the working synergy between the two design partners. Customers also need to feel confident in their IC supplier's ability to control the manufacturing and testing processes, thereby ensuring quality, reliability, and consistent delivery.

Allegro is exceptionally positioned to serve each customer's system requirements with either application-specific custom products or a broad spectrum of standard products. The measure of our success is your total satisfaction.

### GENERAL INFORMATION

#### **DEFINITION OF TERMS**

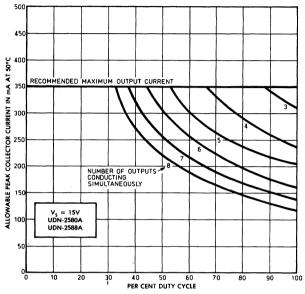

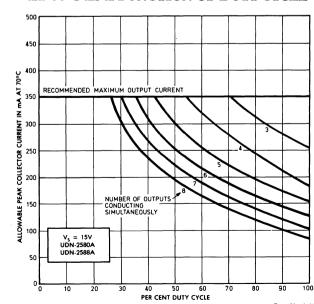

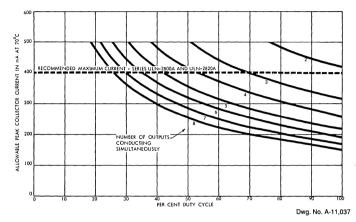

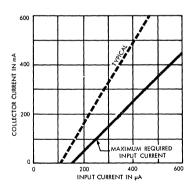

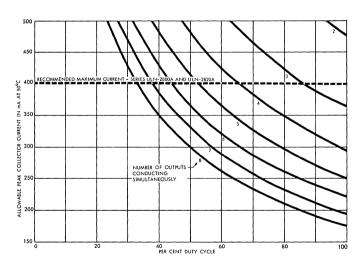

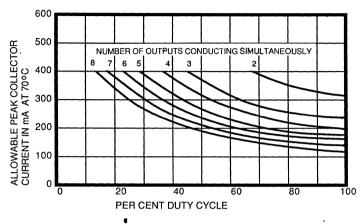

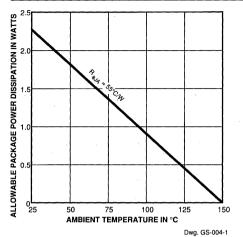

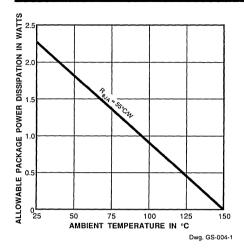

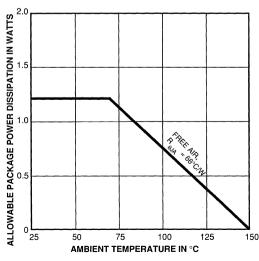

ABSOLUTE MAXIMUM RATINGS are limiting values of operation and should not be exceeded under the worst conditions. These values are chosen to provide acceptable serviceability of the device. The equipment manufacturer should design so that initially, and throughout life, no absolute maximum value is exceeded. If exceeded, even if the device continues to operate, its life may be considerably shortened.

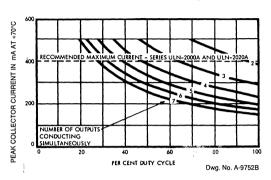

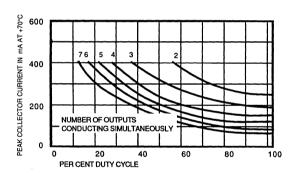

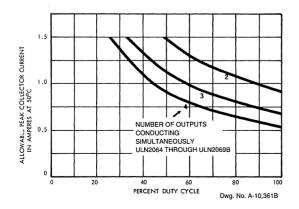

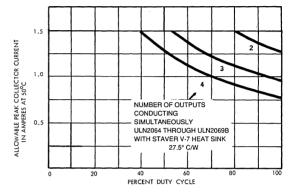

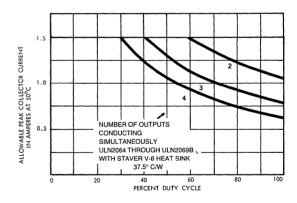

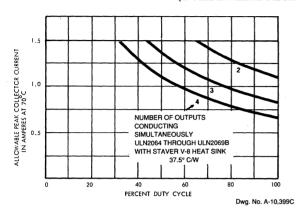

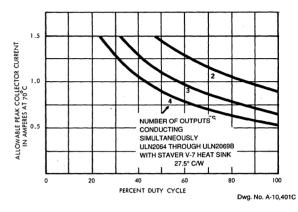

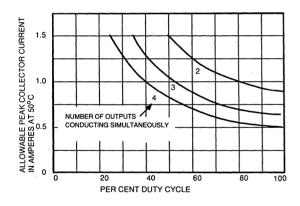

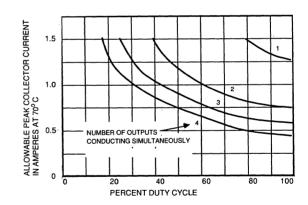

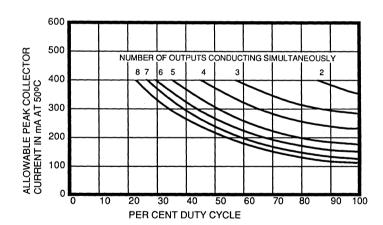

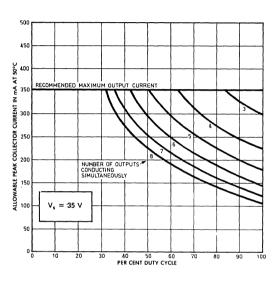

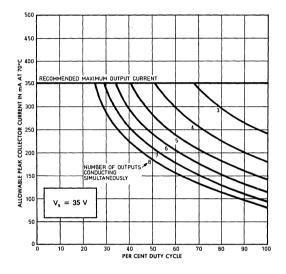

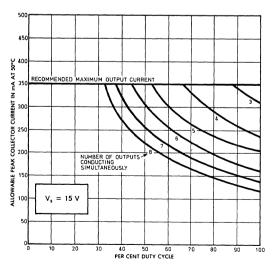

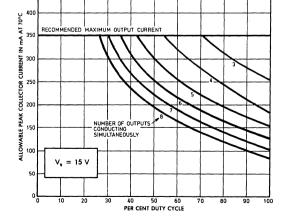

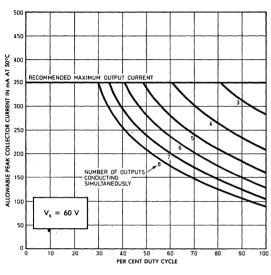

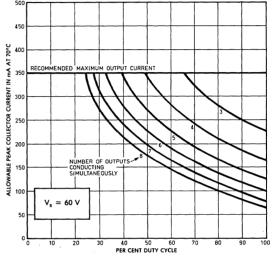

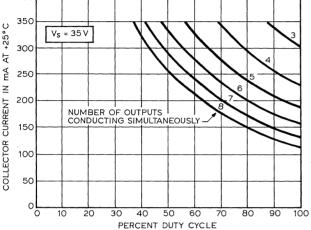

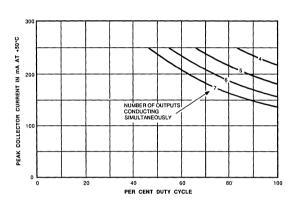

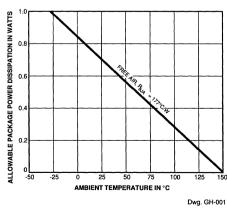

The absolute maximum output current ratings are the maximum allowable under any condition. In application, output current will be limited by number of outputs conducting, duty cycle and timing, ambient temperature, heat sinking and/or forced cooling, and other heat sources.

Under any set of conditions, the specified maximum junction temperature (usually +150°C) should not be exceeded. In those devices which include an internal thermal shutdown, fault conditions which produce excessive junction temperature will activate device thermal shutdown circuitry. These conditions can be tolerated, but should be avoided.

**TYPICAL CHARACTERISTICS** are given for circuit design information only and, unless otherwise stated, are usually given at the nominal operating voltage and an ambient temperature of +25°C. Although these values are indicative of the peak distribution for a large number of production lots, these values should not be construed as guaranteed for any particular device or production lot.

**CHARACTERISTICS LIMITS** are those values that are guaranteed under the test conditions shown.

The absolute magnitude convention is used for **Electrical Characteristics Limits** where the limits are defined as:

maximum [minimum] limit: the greater [smaller] magnitude limit of a range of like-signed values; if the range includes both positive and negative values, both limiting values are maximums [the minimum is implicitly zero].

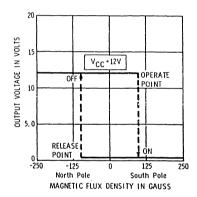

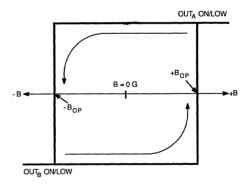

The algebraic convention is used for **Magnetic Characteristics Limits** where negative flux densities are defined as less than zero.

The minimum value is therefore the most negative value, the maximum value is the most positive value, and zero has no special significance.

**RECOMMENDED OPERATING CONDITIONS** are given for optimum device performance. Operation outside these conditions is permitted (within the Absolute Maximum Ratings) without any implied guarantee of level of performance.

It is recommended that equipment manufacturers consult their local sales office whenever device applications involve unusual electrical, mechanical, or environmental operating conditions.

#### **DEFINITION OF TERMS**

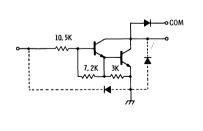

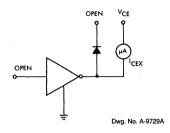

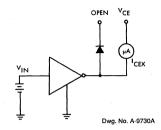

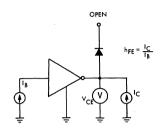

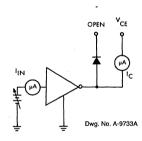

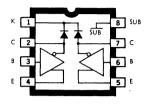

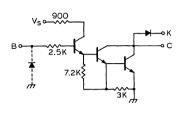

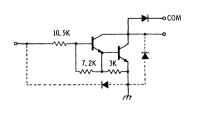

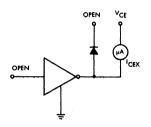

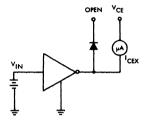

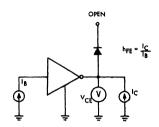

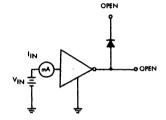

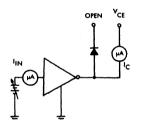

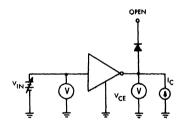

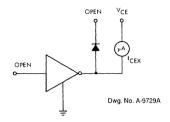

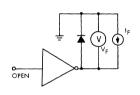

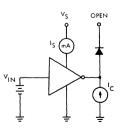

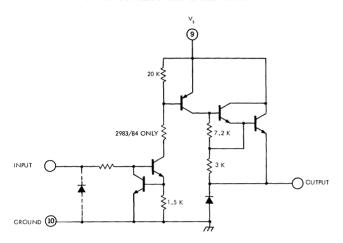

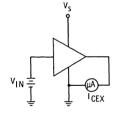

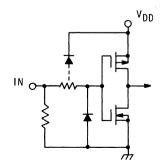

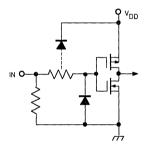

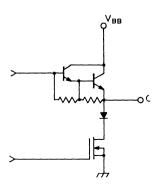

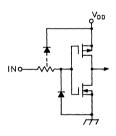

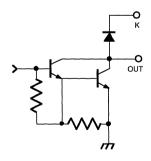

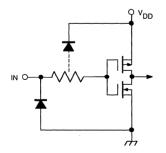

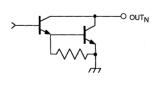

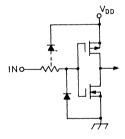

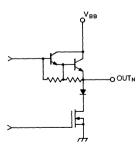

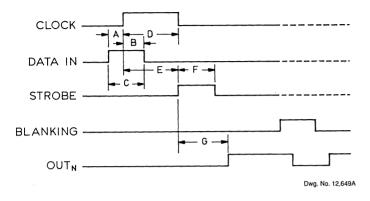

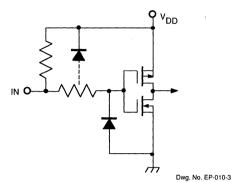

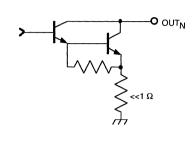

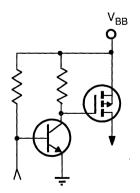

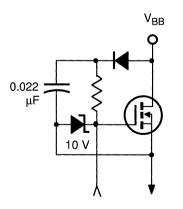

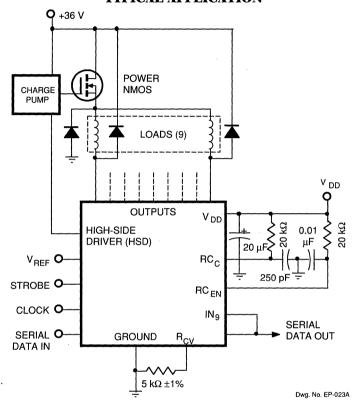

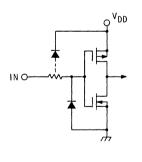

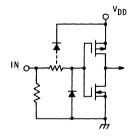

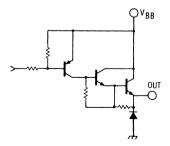

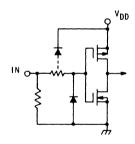

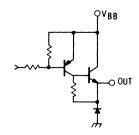

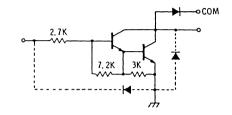

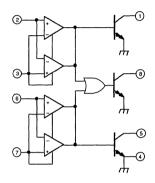

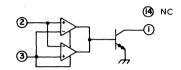

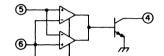

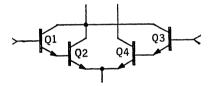

SPECIAL SYMBOLS are sometimes used to simplify circuit drawings.

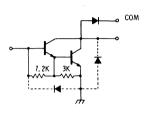

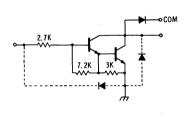

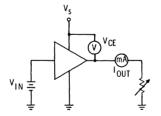

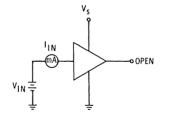

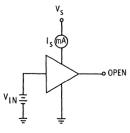

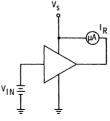

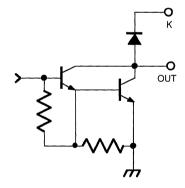

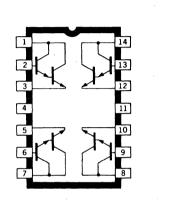

Transistor

Dwg. No. OA-001

**ADVANCE INFORMATION** is used to advise customers of proposed additions to the product line. The specifications given are target or goal specifications and may, therefore, change without notice. Allegro MicroSystems, Inc. reserves the right to not manufacture these proposed devices which have been announced as "advance information". Contact your local sales office for details of current status and latest specifications.

**PRELIMINARY INFORMATION** is issued to advise customers of additions to the product line which, nevertheless, still have "pre-production" status. Details may, therefore, change without notice although it is expected that the performance data is representative of "full production" status. Contact your local sales office for details of current status and latest specifications.

#### IMPORTANT NOTICE

Allegro MicroSystems, Inc., reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Changes and improvements made after the publication of this catalog will be reflected in updated data sheets or other literature as soon as possible. Components made under military approvals will be in accordance with the approval requirements.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Allegro MicroSystems, Inc. reserves the right to discontinue any device without notice.

Before placing an order, Allegro advises its customers to obtain the latest version of the relevant information to verify that the information being relied upon is current.

Allegro products are not intended for use in life support appliances, devices, or systems. Use of an Allegro product in such applications without the written consent of Allegro MicroSystems, Inc. is prohibited.

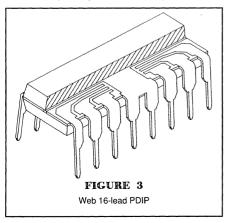

## PACKAGE DESIGNATORS

**A** (DIP) 14 to 40 pins

Dwg. OA-004-18

**B** (Semi-Tab DIP) 8 to 24 pins

Dwg. OA-004-17

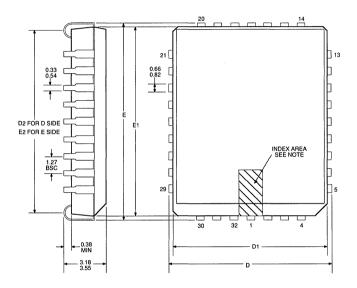

EA (One-Semi-Tab PLCC) 28 leads EB (Semi-Tab PLCC) 28 or 44 leads EP (Sq. PLCC) 20, 28, or 44 leads EQ (Rect. PLCC) 32 (7 x 9) leads

Dwg. OA-007-44

K (SIP) 4 pins KA (SIP) 5 pins

Dwg. OA-013-4

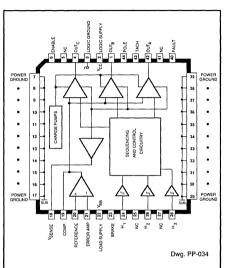

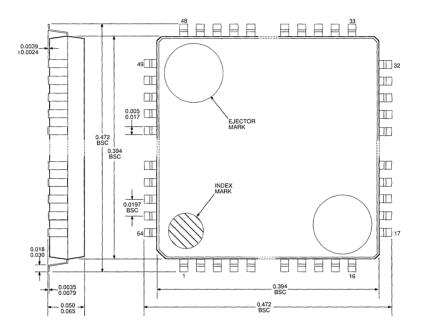

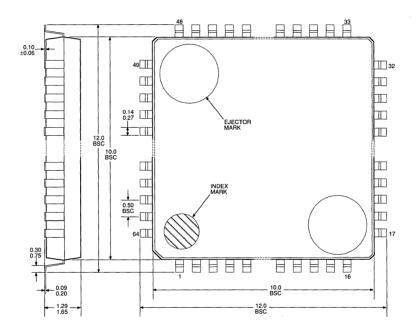

JT (Thin Quad Flatpack) 64 leads

Dwg. OA-014-64

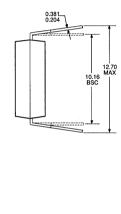

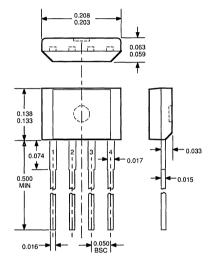

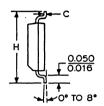

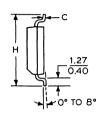

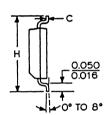

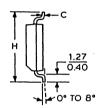

LL, LR, or LT (SOT)

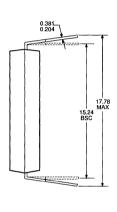

Dwg. OA-008-3

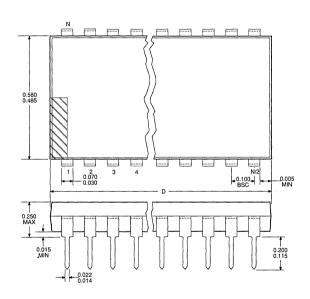

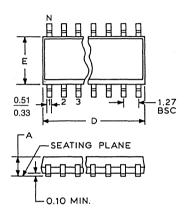

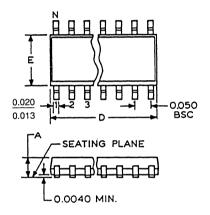

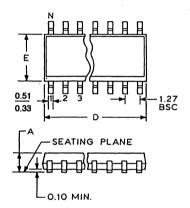

L (SOIC) 8, 14, or 16 leads

Dwg. OA-005-14

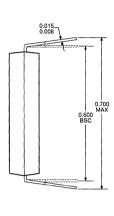

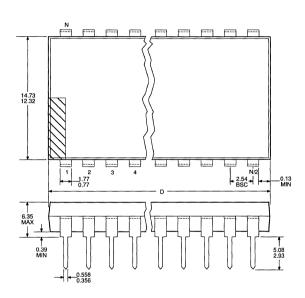

LB (Semi-Tab SOIC) 20 or 24 leads LW (Wide-Body SOIC) 16 to 28 leads

Dwg. OA-005-21

THE PROPERTY OF THE PARTY OF TH

Dwg. OA-005-17

M (DIP) 8 pins

Dwg. OA-004-8

U

Dwg. OA-015-3

Dwg. OA-015-4

W (Power-Tab SIP) 12 leads

Dwg. OA-006-12

Z (Power-Tab SIP) 5 leads

Dwg. OA-006-5

### DEVICE PART-NUMBERING

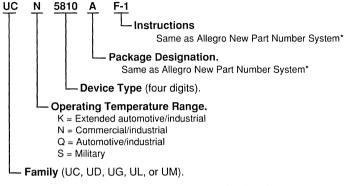

#### ALLEGRO MICROSYSTEMS NEW PART NUMBERS

8958 Instructions (optional; in the order listed). A = Revision, see detail specification F = Active pull-down device (BiMOS only) -1 = (Any number except 883) Selected version, see detail specification BU = Burned-In device\* BS = Compliant, with screening to BS9493\* TR = Tape and reel (surface-mount devices only) Package Designation. A = Plastic, dual in-line B = Plastic, dual in-line semi-tab C = Unpackaged chip † EA = Plastic, leaded chip carrier, one semi-tab EB = Plastic, leaded chip carrier, two semi-tabs EP = Plastic, leaded chip carrier, square EQ = Plastic, leaded chip carrier, rectangular JT = Plastic, thin quad flatpack, 64 leads K = Plastic, 4-lead mini-SIP KA = Plastic, 5-lead mini-SIP L = Plastic, SOIC LB = Plastic, wide-body SOIC power tab LL = Plastic, SOT-89, long-lead version LR = Plastic, SOT-23/TO-236AB LT = Plastic SOT-89/TO-243AA LW = Plastic, wide-body SOIC M = Plastic, 8-pin mini-DIP T = Plastic, 3-lead mini-SIP U = Plastic, 3-lead thin mini-SIP UA = Plastic, short 3-lead thin mini-SIP W = Plastic, 12-lead single in-line power tab WH = W Package with 18 formed leads, horizontal mount WV = W Package with 18 formed leads, vertical mount X = Special Z = Plastic, 5-lead single in-line power tab (TO-220) Operating Temperature Range. C = Commercial (0°C to +70°C) S = Standard (-20°C to +85°C) E = Extended automotive/industrial (-40°C to +85°C) K = Industrial/military (-40°C to +125°C)L = Automotive/military (-40°C to +150°C)  $M = Military (-55^{\circ}C to +125^{\circ}C)$ X =Special (i.e., wafer probe at +25°C only) Device Type (four digits).

#### Allegro MicroSystems Identifier.

- \* Instruction suffix 'BU' available only with temperature codes 'S', 'E', 'K, or 'L'; suffix 'BS' available only through European sales office.

- † Discrete and integrated circuit chips are described in Brochure CN-193.

All possible combinations of device type, operating temperature range, and package style are not necessarily available. Consult individual device specifications or sales office for complete information.

### **DEVICE PART-NUMBERING**

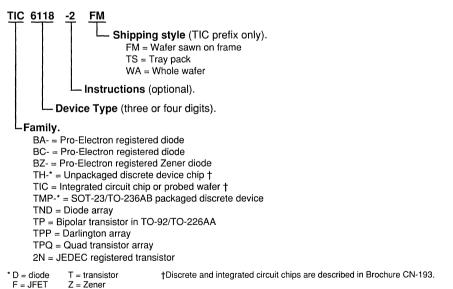

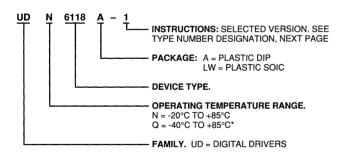

#### ORIGINAL SPRAGUE SEMICONDUCTOR GROUP PART NUMBERS

- Instruction suffix 'BU' available only with temperature codes 'N' or 'Q'; suffix 'BS' available only through European sales office.

- † Discrete and integrated circuit chips are described in Brochure CN-193.

#### ORIGINAL SPRAGUE SEMICONDUCTOR GROUP PART NUMBERS

All possible combinations of device type, operating temperature range, and package style are not necessarily available. Consult individual device specifications or sales office for complete information.

### GENERAL INFORMATION

#### ORDERING INFORMATION

To place an order, obtain price and delivery information, or to request technical literature, contact your local Allegro sales office or sales representative. See back of book, or:

From United States

and Canada

Allegro MicroSystems, Inc.

115 Northeast Cutoff

Box 15036

Worcester, MA 01615 Tel: (508) 853-5000 Fax: (508) 853-5049

From Europe and Mideast

Allegro MicroSystems Europe Ltd. Balfour House, Churchfield Road

Walton-on-Thames, Surrey KT12 2TD

UNITED KINGDOM Tel: (44-932) 253-355 Fax: (44-932) 246-622

From Asia

Allegro MicroSystems, Inc.

115 Northeast Cutoff

Box 15036

Worcester, MA 01615 Tel: (508) 853-5000 Fax: (508) 853-5049

### TECHNICAL ASSISTANCE

Requests for additional technical information or applications assistance should be referred to your local Allegro sales office or sales representative. See back of book, or:

Allegro MicroSystems, Inc. 115 Northeast Cutoff

Box 15036

Worcester, MA 01615 Tel: (508) 853-5000 Fax: (508) 853-5049

# INTEGRATED CIRCUITS AND TRANSISTOR ARRAYS

### PRODUCT INDEX IN NUMERICAL ORDER\*

See Section 7 for Index to Discrete Devices

| Part Number *  | Description                               | Page  |

|----------------|-------------------------------------------|-------|

| 06 thru 56     | Quad Transistor Arrays                    | 7-35  |

| 903 thru 942   | Multiple Diode Arrays                     | 7-31  |

| 2001 thru 2024 | 7-Channel, High-Current Darlington Arrays | 3-1   |

|                | Reliability Report                        | 8-9   |

| 2061 thru 2069 | 1.5 A Darlington Switches                 | 3-9   |

| 2222           | Quad NPN Transistor Array                 | 7-34  |

| 2429           | Fluid Detector                            | 6-1   |

| 2436           | Dual-Mode (10 min/5 min) Countdown Timer  | 6-4   |

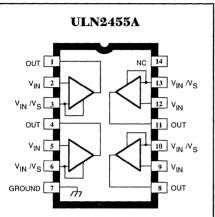

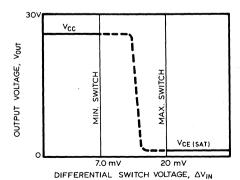

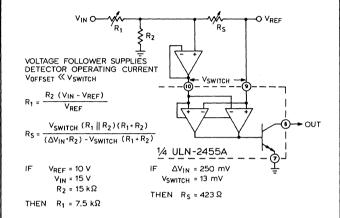

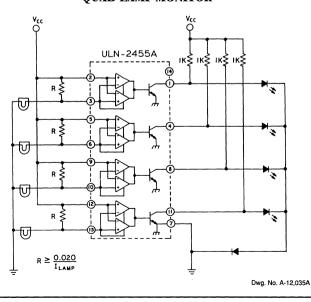

| 2454 and 2455  | Automotive Lamp Monitors/Comparators      | 6-7   |

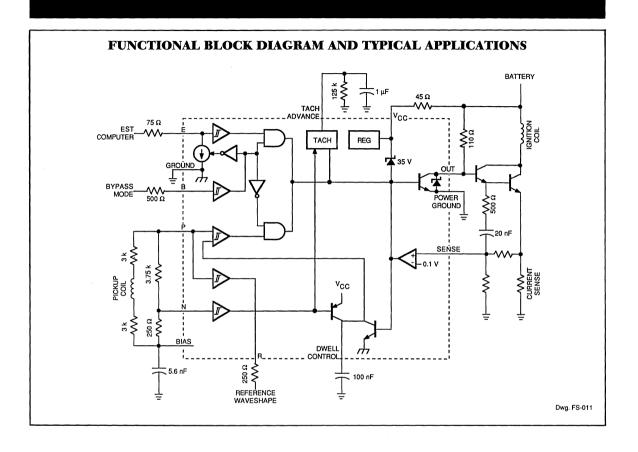

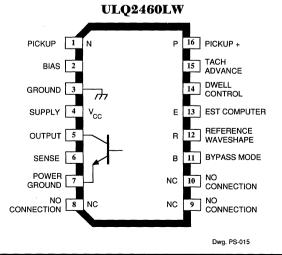

| 2460           | Electronic Spark Timing                   | 6-11  |

| 2540           | Quad 1.8 A Darlington Power Driver        | 3-18  |

| 2543           | Quad Protected Darlington Power Driver    | 3-21  |

| 2544           | Quad 1.8 A Darlington Power Driver        | 3-25  |

| 2547           | Quad Protected Darlington Power Driver    | 3-28  |

| 2549           | Quad Protected Darlington Power Driver    | 3-32  |

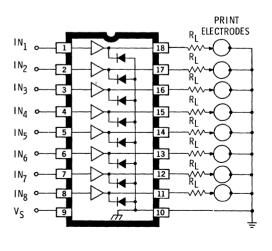

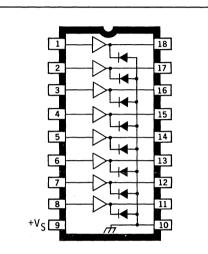

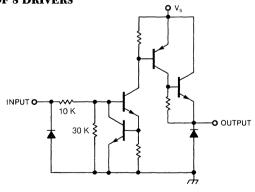

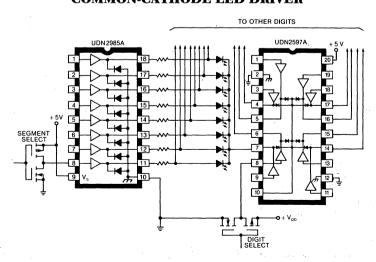

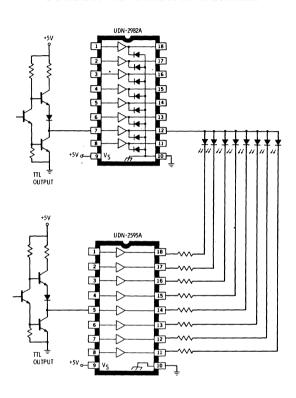

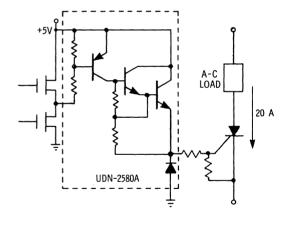

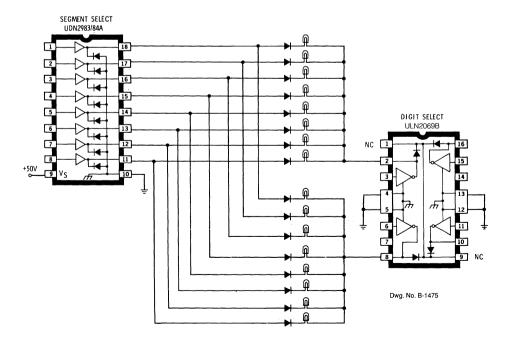

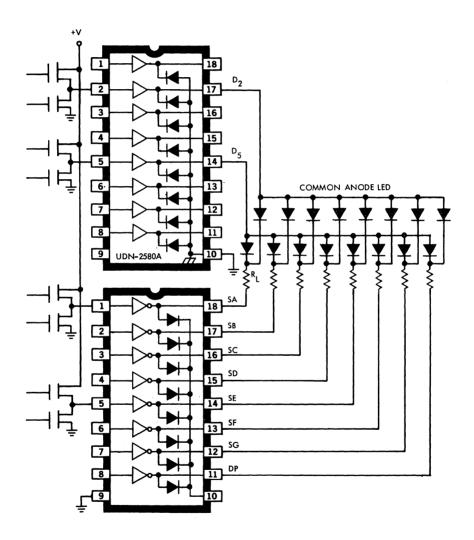

| 2580           | 8-Channel, High-Current Source Driver     | 3-36  |

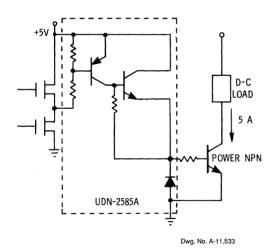

| 2585           | 8-Channel, Saturated Source Driver        | 3-36  |

| 2588           | 8-Channel, High-Current Source Driver     | 3-36  |

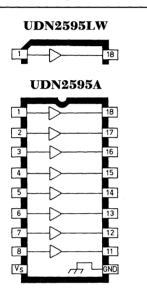

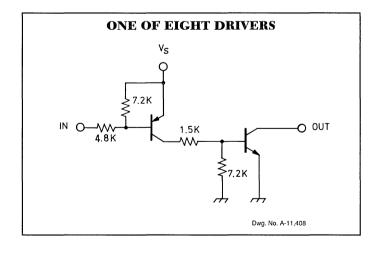

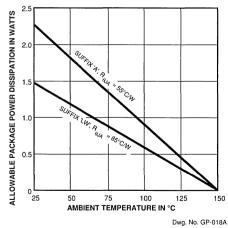

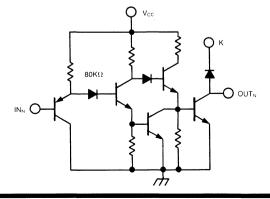

| 2595           | 8-Channel, Saturated Sink Driver          | 3-44  |

| 2596 and 2597  | 8-Channel, Saturated Sink Drivers         | 3-46  |

| 2801 thru 2823 | 8-Channel, High-Current Darlington Arrays | 3-48  |

|                | Reliability Report                        | 8-9   |

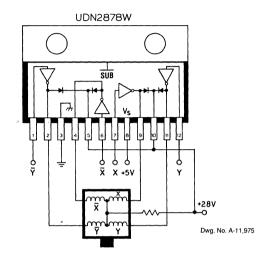

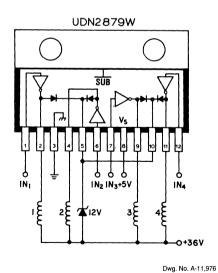

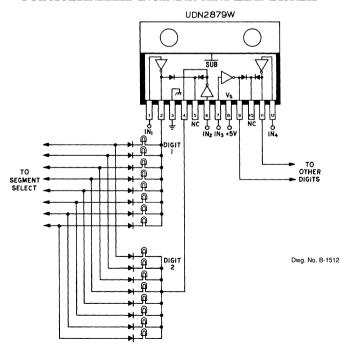

| 2878 and 2879  | Quad 4 A Darlington Switches              | 3-56  |

| 2907           | Quad PNP Transistor Array                 | 7-34  |

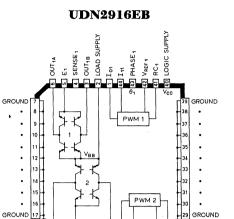

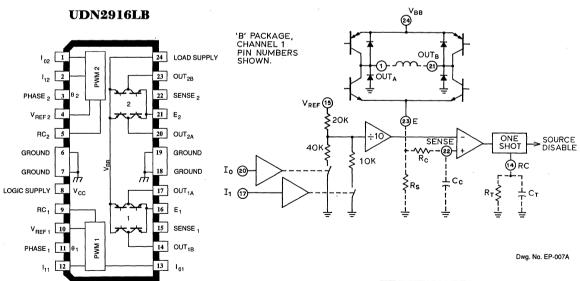

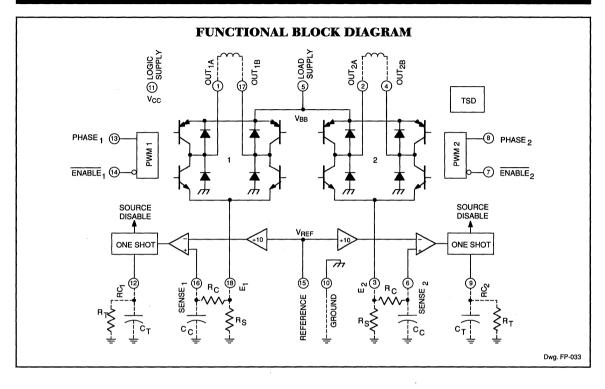

| 2916           | Dual Full-Bridge PWM Motor Driver         | 3-61  |

| 2917           | Dual Full-Bridge PWM Motor Driver         | 3-66  |

| 2918           | Dual Full-Bridge PWM Motor Driver         | 3-71  |

| 2936           | 3-Phase ±2 A Brushless DC Motor Drivers   | 3-76  |

|                | Description and Application               | 3-249 |

| 2943           | High-Current Half-Bridge Motor Driver     | 3-84  |

| 2944           | Quad 4 A High-Voltage Source Driver       | 3-88  |

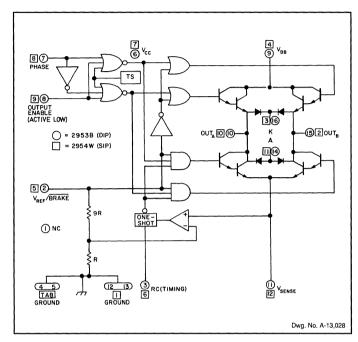

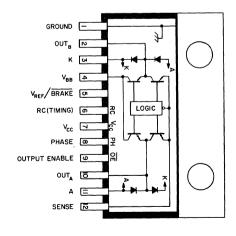

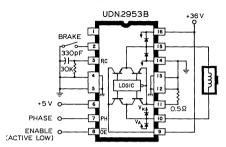

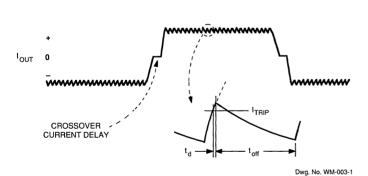

| 2953 and 2954  | 2 A Full-Bridge PWM Motor Drivers         | 3-91  |

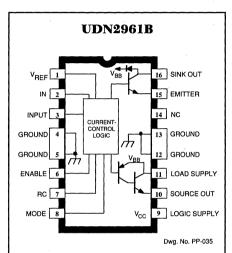

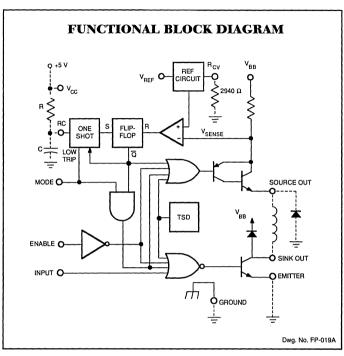

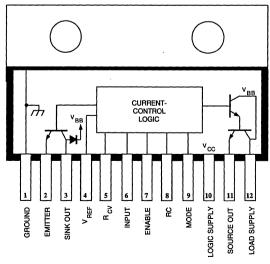

| 2961           | 3.4 A PWM Printhead/Motor Driver          | 3-96  |

| 2962           | Dual 3 A PWM Solenoid/Motor Driver        | 3-101 |

| 2981 thru 2984 | 8-Channel, Source Drivers                 | 3-106 |

| 2985           | 8-Channel, Saturated Source Driver        | 3-111 |

Complete part number includes additional characters to indicate operating temperature range and package style.

See detailed specification.

### ICs AND TRANSISTOR ARRAYS PRODUCT INDEX IN NUMERICAL ORDER

| Part Number *      | Description                                                            | Page     |

|--------------------|------------------------------------------------------------------------|----------|

| 2987               | 8-Channel, Short-Circuit Protected Source Driver                       | 3-113    |

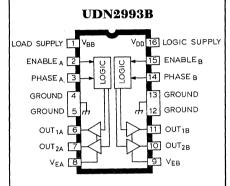

| 2993               | Dual Full-Bridge Motor Driver                                          | 3-117    |

| 2998               | Dual 2 A Full-Bridge Motor Driver                                      | 3-121    |

| 3046               | Zero-Speed Hall-Effect Gear-Tooth Sensors                              | 4-1      |

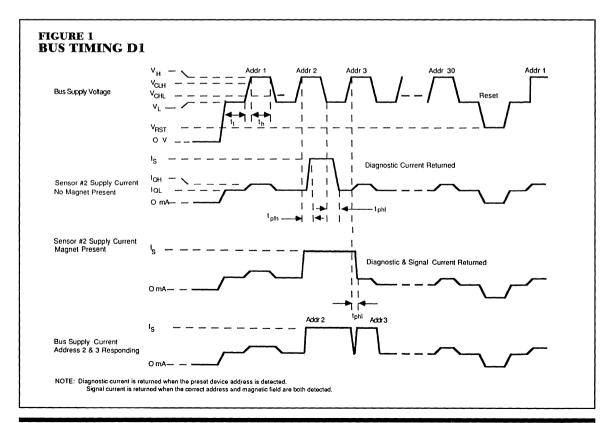

| 3055               | Multiplexed Two-Wire Hall-Effect Sensor IC                             | 4-8      |

| 3056 and 3058      | Zero-Speed Hall-Effect Gear-Tooth Sensors                              | 4-1      |

| 3059               | AC Coupled Hall-Effect Gear-Tooth Sensor                               | 4-16     |

| 3113               | Hall-Effect Switch                                                     | 4-20     |

| 3119               | Hall-Effect Switch                                                     | See 3121 |

| 3120               | Hall-Effect Switch                                                     | 4-20     |

| 3121, 3122, & 3123 | Hall-Effect Switches for High-Temperature Operation                    | 4-24     |

| 3130               | Hall-Effect Switch                                                     | 4-20     |

| 3132 and 3133      | Ultra-Sensitive Bipolar Hall-Effect Switches                           | 4-29     |

| 3140               | Hall-Effect Switch                                                     | 4-20     |

| 3141, 3142, & 3143 | Sensitive Hall-Effect Switches for High-Temperature Operation          | 4-34     |

| 3175 and 3177      | Hall-Effect Digital Latches                                            | 4-35     |

| 3185 thru 3189     | Hall-Effect Latches for High-Temperature Operation                     | 4-38     |

| 3235               | Dual Output Hall-Effect Digital Switch                                 | 4-42     |

| 3275               | Complementary Output Hall-Effect Latch                                 | 4-46     |

| 3501               | Linear Output Hall-Effect Sensor                                       | 4-48     |

| 3503               | Ratiometric, Linear Hall-Effect Sensor                                 | 4-52     |

| 3506 and 3507      | Ratiometric, Linear Hall-Effect Sensors for High-Temperature Operation | 4-56     |

| 3625 and 3526      | Power Hall Sensor/Drivers for Brushless DC Motors                      | 4-57     |

| 3718               | Low-Voltage Audio Power Amplifier                                      | 6-16     |

| 3751               | Power Operational Amplifier                                            | 3-125    |

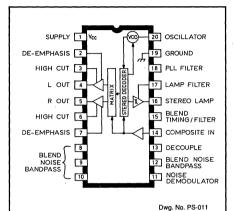

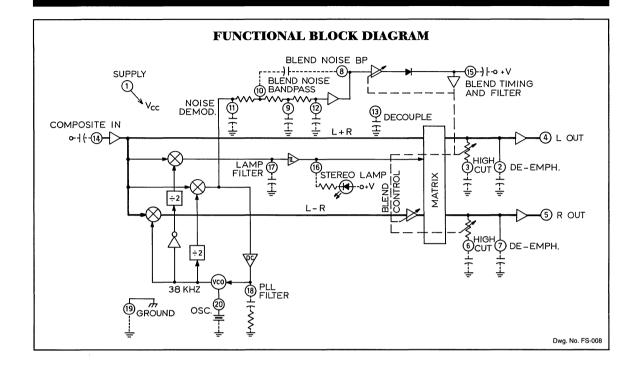

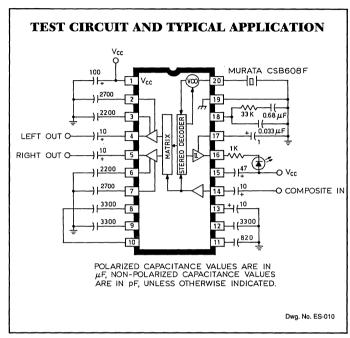

| 3827               | FM Stereo Decoder with Noise-Actuated Blend                            | See 3828 |

| 3828               | FM Stereo Decoder with Noise-Actuated Blend                            | 6-20     |

| 3841               | AM Signal Processor                                                    | 6-25     |

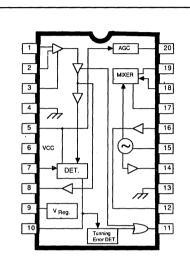

| 3844               | Dual-Conversion AM Receiver                                            | 6-32     |

| 3845 and 3846      | AM Noise Blankers                                                      | 6-34     |

| 3847               | Dual-Conversion AM Receiver                                            | See 3844 |

| 3848               | Dual-Conversion AM Receiver                                            | 6-41     |

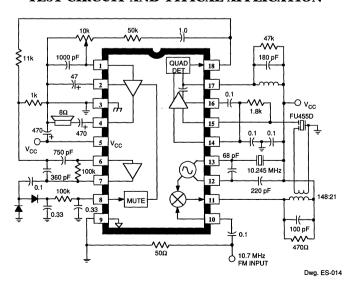

| 3859               | FM Communications IF System                                            | 6-43     |

| 3883               | FM Communications IF and Audio System                                  | 6-45     |

| 3904 and 3906      | Quad Transistor Arrays                                                 | 7-34     |

| 4000               | Medium-Power Quad Darlington Array                                     | 7-32     |

| 5140               | Protected PowerHall Sensor Lamp/Solenoid Driver                        | 4-63     |

| 5275               | Complementary Output Hall-Effect Latched Driver                        | 4-70     |

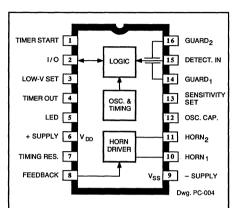

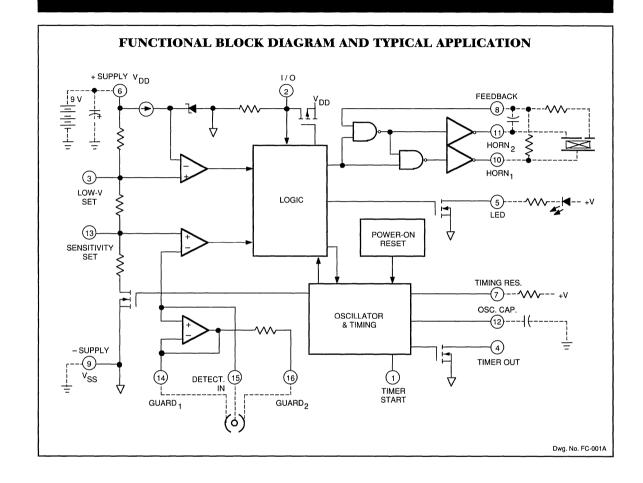

| 5348               | Smoke Detector with Interconnect and Timer                             | 6-48     |

| 5401               | Quad PNP Transistor Array                                              | 7-34     |

| 5616               | Liquid Crystal Display Automotive Clock                                | 6-55     |

<sup>\*</sup> Complete part number includes additional characters to indicate operating temperature range and package style. See detailed specification.

### ICs AND TRANSISTOR ARRAYS PRODUCT INDEX IN NUMERICAL ORDER

| Part Number *  | Description                                                    | Page       |

|----------------|----------------------------------------------------------------|------------|

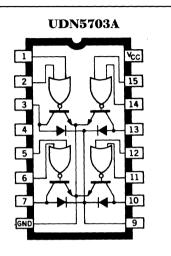

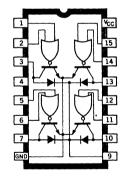

| 5703 and 5706  | Quad Peripheral and Power Drivers                              | 3-129      |

| 5713           | Dual OR Peripheral and Power Driver                            | 3-133      |

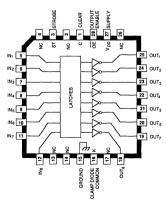

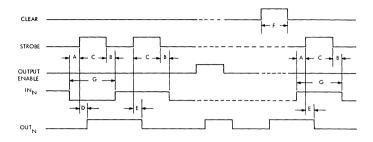

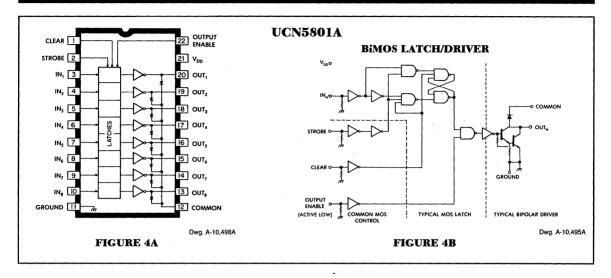

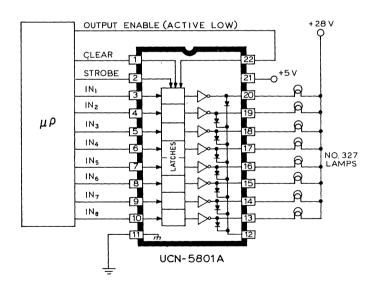

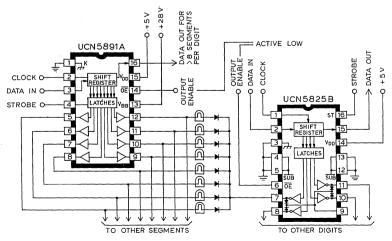

| 5800 and 5801  | High-Speed BiMOS Latched Drivers                               | 3-136      |

|                | Reliability Report                                             | 8-14       |

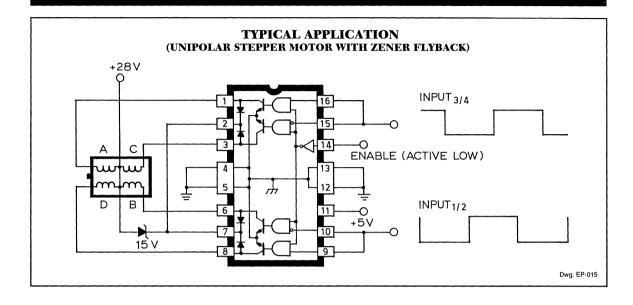

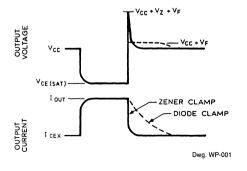

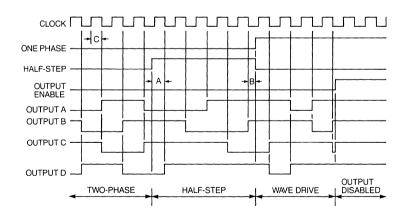

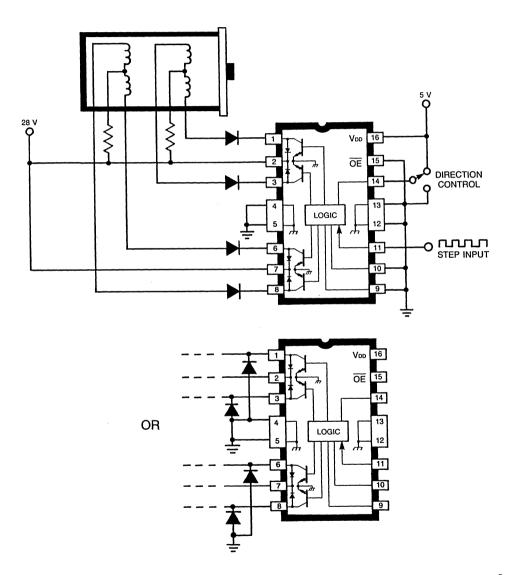

| 5804           | 1.25 A, Unipolar Stepper-Motor Translator/Driver               | 3-141      |

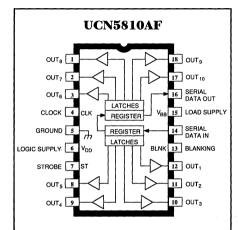

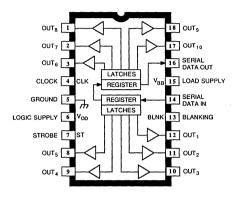

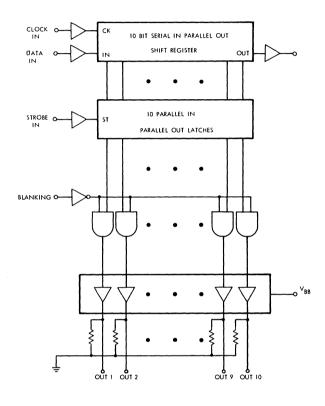

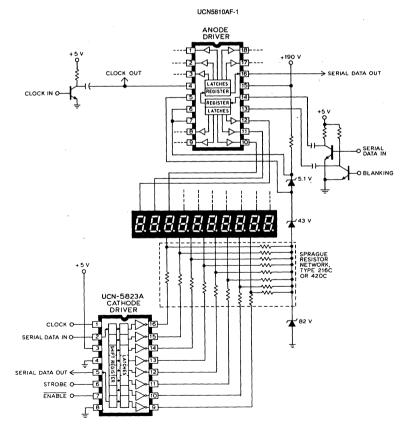

| 5810           | 10-Bit High-Speed Serial-In, Latched Source Driver             | See 5810-F |

| 5810-F         | 10-Bit Serial-In, Latched Source Drivers with Active Pulldowns | 3-146      |

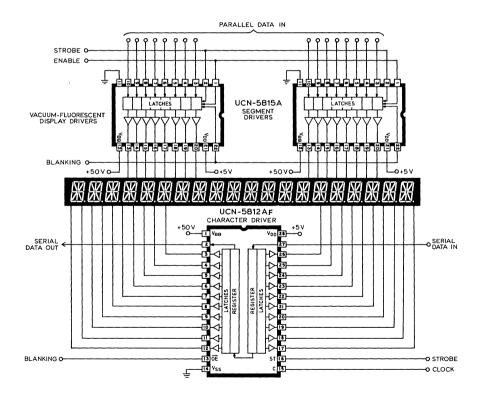

| 5811           | 12-Bit High-Speed Serial-In, Latched Driver                    |            |

| 5812-F         | 12-Bit Serial-In, Latched Source Drivers with Active Pulldowns | 3-154      |

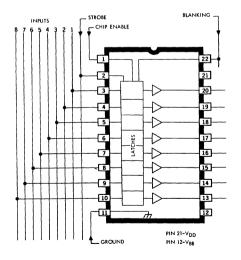

| 5815           | 8-Bit High-Speed Latched Source Driver                         | 3-158      |

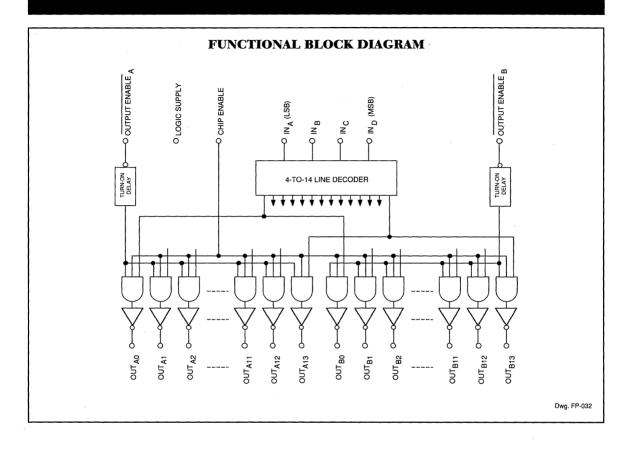

| 5816           | Addressable, Latched 16-Channel Driver                         | 3-161      |

| 5817           | Addressable, 28-Line Decoder/Driver                            | 3-165      |

| 5818-F         | 32-Bit Serial-In, Latched Source Drivers with Active Pulldowns | 3-170      |

| 5821 thru 5823 | 8-Bit High-Speed Serial-In, Latched High-Voltage Drivers       | 3-174      |

| 5829           | 9-Bit Serial-In, Latched 1.6 A Driver                          | 3-178      |

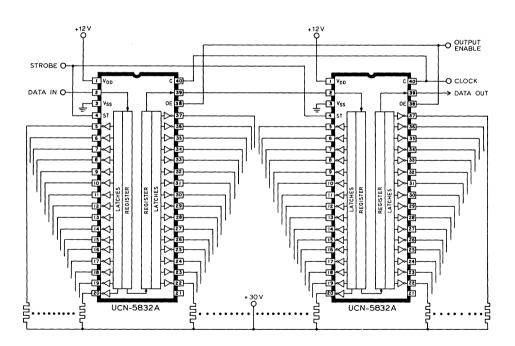

| 5832           | 32-Bit Serial-In, Latched Sink Driver                          | 3-187      |

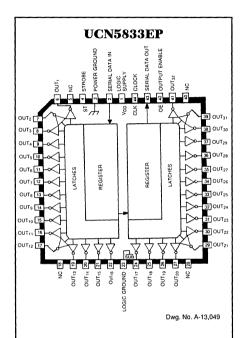

| 5833           | 32-Bit Serial-In, Latched Darlington Driver                    | 3-191      |

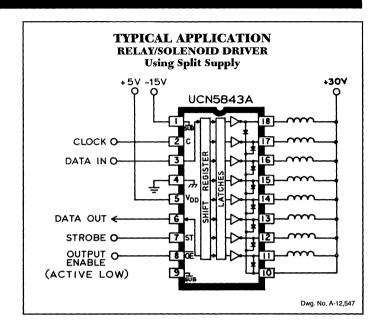

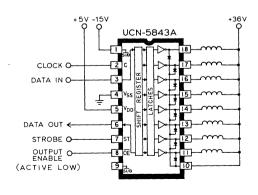

| 5841 thru 5843 | 8-Bit Serial-In, Latched High-Voltage Drivers                  | 3-195      |

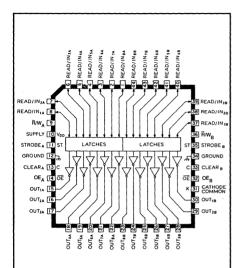

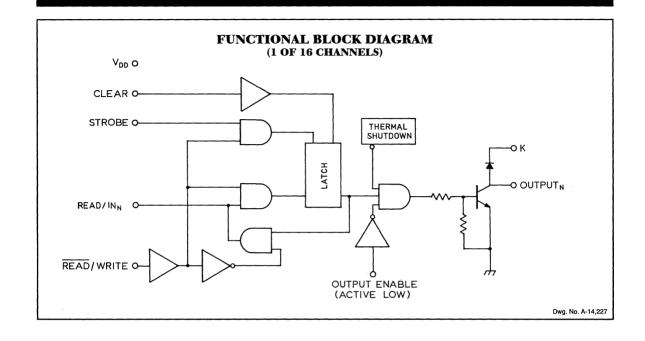

| 5881           | Dual 8-Bit Latched Driver with Read Back                       | 3-200      |

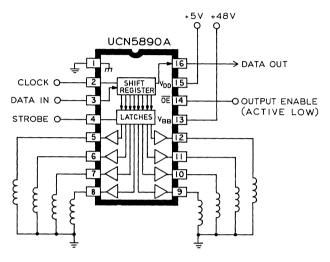

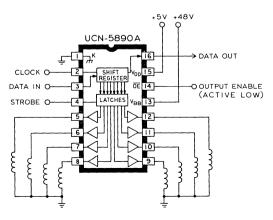

| 5890 and 5891  | 8-Bit Serial-In, Latched Source Drivers                        | 3-203      |

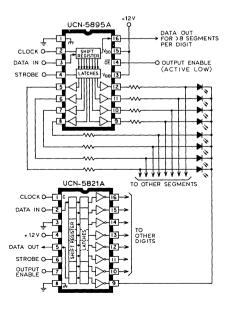

| 5895           | 8-Bit Serial-In, Latched Source Driver                         | 3-208      |

| 6002           | Dual Complementary-Pair Transistor Array                       | 7-34       |

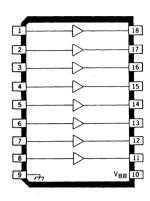

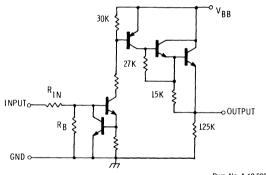

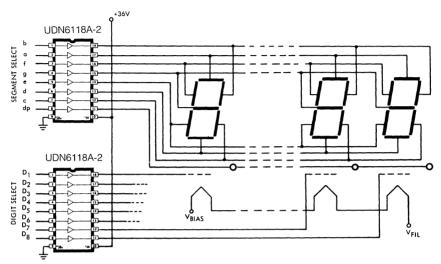

| 6116 and 6118  | Vacuum Fluorescent Display Drivers                             | 3-213      |

|                | Reliability Report                                             | 8-19       |

| 6427           | Quad NPN Transistor Array                                      | 7-34       |

| 6502 and 6700  | Dual Complementary-Pair Transistor Arrays                      | 7-34       |

| 7003           | 7-Channel, 150 V Darlington Array                              | 3-218      |

| 8131           | Precision Supervisory Systems Monitor                          | 6-61       |

| 8181           | Low-Dropout, 5 V Regulator                                     | 6-66       |

| 8901           | 3-Phase Brushless DC Motor Back-EMF Controller/Driver          | 5-1        |

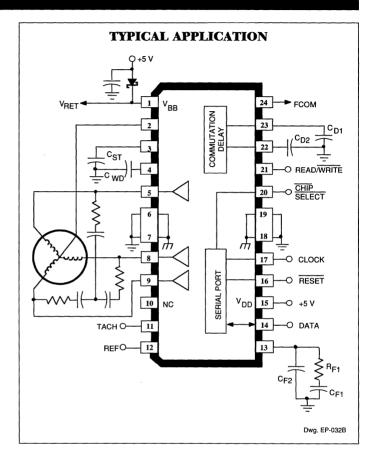

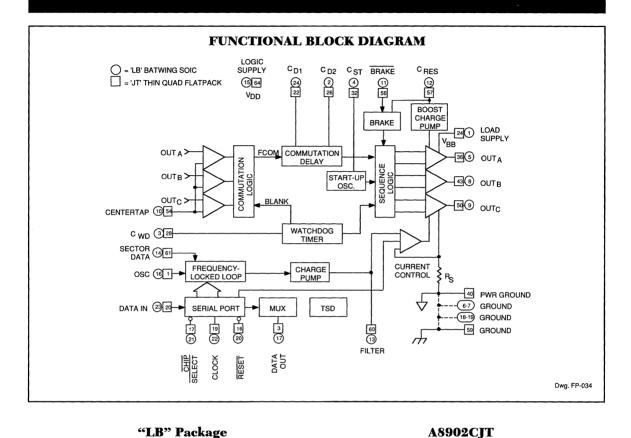

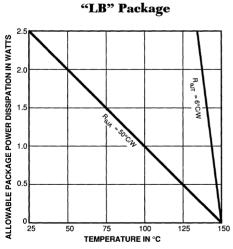

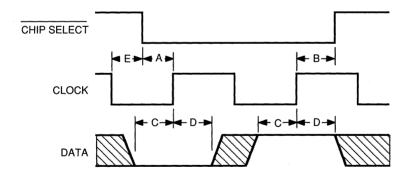

| 8902           | 3-Phase Brushless DC Motor Back-EMF Controller/Drivers         | 5-11       |

| 8920           | Dual Schottky Diode                                            | 5-21       |

| 8925           | 3-Phase ±4 A Brushless DC Motor Controller/DMOS Driver         |            |

| 8932           | 5 V MOS Voice Coil Motor Driver                                | See 8932-A |

| 8932-A         | 5 V MOS Voice Coil Motor Driver                                | 5-28       |

| 8936           | 5 V MOS Voice Coil Motor Driver                                | 5-35       |

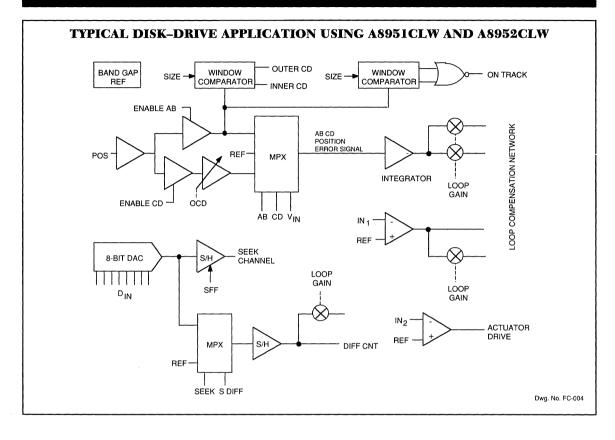

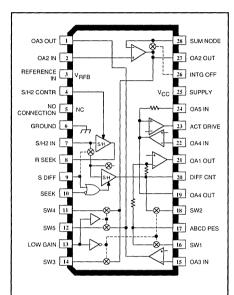

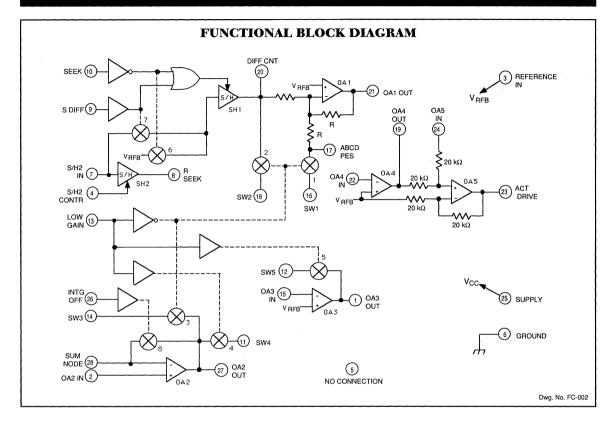

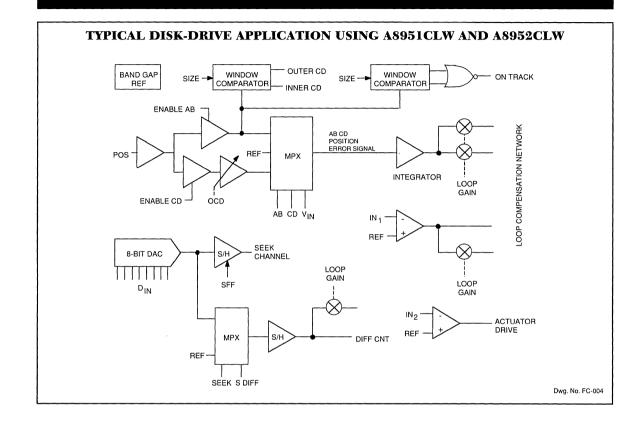

| 8951           | Servo Controller System                                        | 5-42       |

| 8952           | Servo Loop Compensator                                         |            |

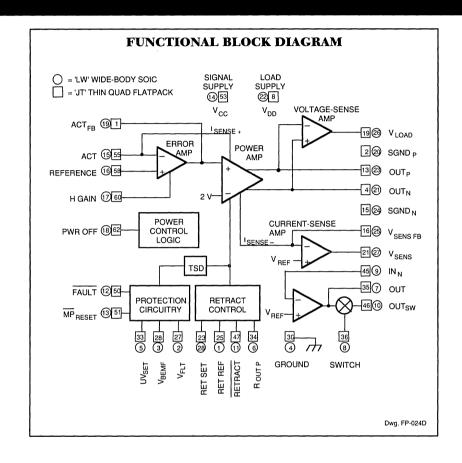

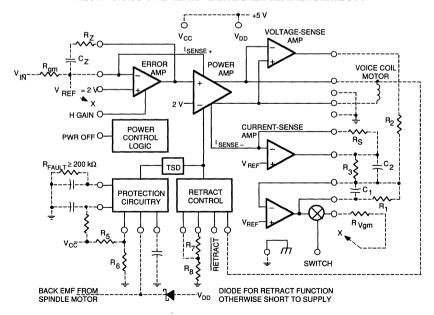

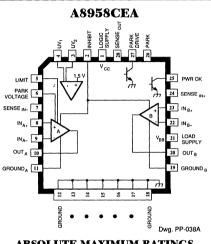

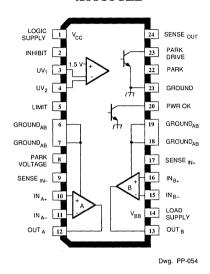

| 8958           | 12 V Voice-Coil Motor Driver                                   | 5-52       |

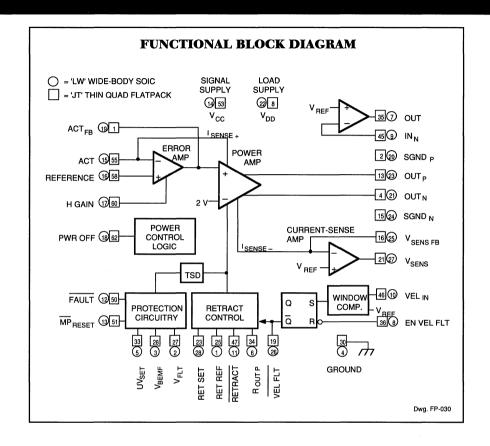

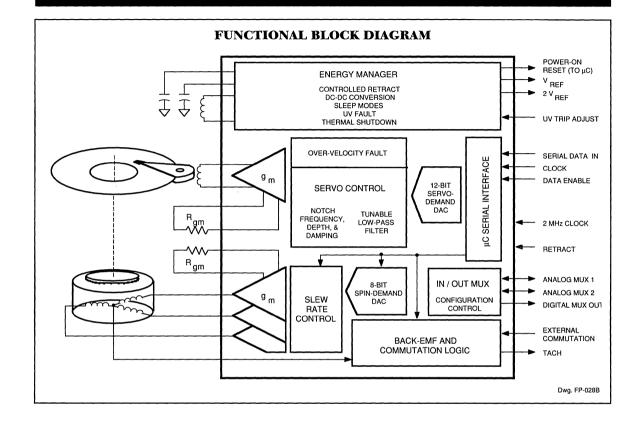

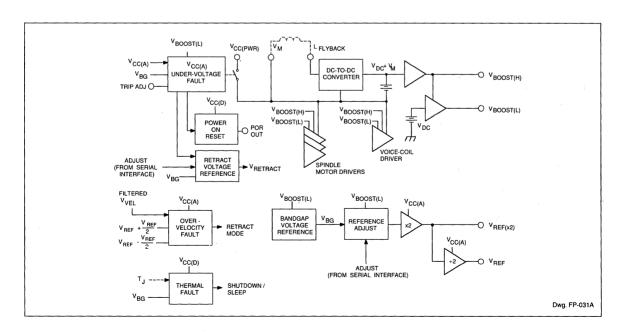

| 8980           | SuperServo Spindle & Voice-Coil Actuation Manager/Driver       | 5-58       |

<sup>\*</sup> Complete part number includes additional characters to indicate operating temperature range and package style. See detailed specification.

### **PRODUCT SELECTION GUIDES**

Parties - Carrier (Carrier Constitution Constitution Constitution Constitution Constitution Constitution Const

MASS STORĀČIE APPĒĪG MIDNIG

AUTOMOTIVE, SIGNAL-PROCESSING, & CONSUMER D

633

DISCRETE TRANSISTURS, DIODES, & ARRAYS

QUALITY & RELLABILITY INFORVESTION

PACKAGE INFORMATION

#### **SECTION 2. PRODUCT SELECTION GUIDES**

| Peripheral Power and Display Drivers                      | 2-1             |

|-----------------------------------------------------------|-----------------|

| High-Voltage (≥80 V) Peripheral Power and Display Drivers | 2-3             |

| BiMOS Intelligent Power Interface Drivers                 | 2-4             |

| Motor Drivers                                             | 2-5             |

| Hall-Effect Sensors                                       | 2-6             |

| Devices for Mass Storage Applications                     | 2-7             |

| Devices for Printer Applications                          | 2-7             |

| Automotive, Signal Processing, and Consumer ICs           | 2-8             |

| Integrated Circuits Cross-Reference                       | 2-10            |

| Competitive Integrated Circuits Part-Numbering Systems    | 2-16            |

| See Also:                                                 |                 |

| Quick Guide to Allegro Discrete Devices                   | 7-1             |

| Discrete Semiconductors Index and Cross Reference         | 7-2             |

| Discrete and Integrated Circuit Semiconductor Chips       | Brochure CN-193 |

#### PERIPHERAL POWER AND DISPLAY DRIVERS

Section 3, unless otherwise indicated

#### IN ORDER OF 1) OUTPUT CURRENT, 2) OUTPUT VOLTAGE, 3) NUMBER OF DRIVERS

| Output Ratings * |     | Features |                 |                    |                |                      |                        |                      |

|------------------|-----|----------|-----------------|--------------------|----------------|----------------------|------------------------|----------------------|

| mA               | ٧   | #        | Serial<br>Input | Latched<br>Drivers | Diode<br>Clamp | Saturated<br>Outputs | Internal<br>Protection | Part Number †        |

| IK DRIVE         | RS  |          |                 |                    |                |                      |                        |                      |

| 100              | 20  | 8        | _               | _                  |                | Х                    | _                      | 2595                 |

|                  | 30  | 32       | X               | X                  | _              | _                    | -                      | 5833                 |

|                  | 40  | 32       | X               | ×                  | -              | Χ                    | -                      | 5832                 |

| 250              | 150 | 7        | _               | _                  | Х              |                      | -                      | 7003                 |

| 300              | 60  | 2        | Hall S          | ensor/Driver       |                | X                    | _                      | 5275 ‡               |

|                  | 45  | 1        | Hall S          | ensor/Driver       | X              | _                    | Х                      | 5140 ‡               |

|                  | 50  | 8        | _               | _                  | X              | Х                    | -                      | 2596                 |

|                  | 80  | 2        | _               | _                  | X              | X                    | _ 1                    | 5713                 |

|                  | 80  | 4        | _               | -                  | X              | X                    | -                      | 5703 and 5706        |

| 350              | 50  | 4        |                 | X                  | X              |                      | -                      | 5800                 |

|                  | 50  | 7        | _               | _                  | Х              | _                    | _ [                    | 2001, 2003, and 2004 |

|                  | 50  | 8        | _               | _                  | X              | _                    | _                      | 2801, 2803, and 2804 |

|                  | 50  | 8        | _               | X                  | X              | _                    | _                      | 5801                 |

|                  | 50  | 8        | Х               | x                  | _              |                      | _ 1                    | 5821                 |

|                  | 50  | 8        | x               | x                  | X              | _                    | _                      | 5841                 |

|                  | 60  | 16       |                 | S-Line Latched     |                | -                    | _                      | 5816                 |

|                  |     | -        |                 |                    | Decodel/Di     | ivei –               | _                      |                      |

|                  | 80  | 8        | X               | X                  |                | _                    | -                      | 5822                 |

|                  | 80  | 8        | X               | X                  | X              | _                    | -                      | 5842                 |

|                  | 95  | 7        | _               | -                  | X              | _                    | -                      | 2023 and 2024        |

|                  | 95  | 8        | -               | -                  | X              | _                    | -                      | 2823                 |

|                  | 100 | 8        | X               | X                  | _              | _                    | -                      | 5823                 |

|                  | 100 | 8        | X               | X                  | X              | _                    |                        | 5843                 |

| 450              | 30  | 28       | Dual 4          | to 14-Line De      | coder/Drive    | r –                  |                        | 5817                 |

| 500              | 50  | 7        |                 |                    | X              | -                    |                        | 2013                 |

| 600              | 60  | 4        |                 |                    | _              | X                    | Х                      | 2547                 |

|                  | 60  | 4        | _               | _                  | Х              | X                    | X                      | 2549                 |

| 700              | 60  | 4        |                 |                    | X              | Х                    | Х                      | 2543                 |

| 750              | 50  | 8        |                 |                    | X              | Х                    | -                      | 2597                 |

| 900              | 14  | 2        | Hall S          | ensor/Driver       | X              | X                    | X                      | 3625‡                |

| 000              | 26  | 2        |                 | ensor/Driver       | X              | X                    | x                      | 3626‡                |

| 1250             | 50  | 4        | Stepp           | er Motor Trans     | lator/Driver   |                      | X                      | 5804                 |

|                  | 50  | 2        | -               | _                  | X              |                      | _                      | 2061                 |

|                  | 50  | 4        | _               | _                  | X              | _                    | _                      | 2064 and 2068        |

| 1500             | 80  | 2        |                 |                    | X              |                      |                        | 2062                 |

| . 500            | 80  | 4        | _               | _                  | X              |                      | _                      | 2065 and 2069        |

| 1600             | 50  | 9        | X               | X                  |                |                      | х                      | 5829                 |

| 1800             | 50  | 4        |                 |                    | X              |                      |                        | 2544                 |

| . 300            | 50  | 4        | -               | -                  | X              | _                    | -                      | 2540                 |

| 4000             | 50  | 4        |                 |                    | X              | _                    | -                      | 2878                 |

|                  | 80  | 4        | _               | _                  | X              | _                    | _ 1                    | 2879                 |

Current is maximum specified test condition, voltage is maximum rating.

See specification for sustaining voltage limits or over-current protection voltage limits.

Continued next page...

<sup>†</sup> Complete part number includes additional characters to indicate operating temperature range and package style.

<sup>‡</sup> Hall-Effect sensor. See Section 4.

### SELECTION GUIDE PERIPHERAL POWER AND DISPLAY DRIVERS

| Output Ratings * |            |    | Features        |                    |                 |                      |                        |               |

|------------------|------------|----|-----------------|--------------------|-----------------|----------------------|------------------------|---------------|

| mA               | v          | #  | Serial<br>Input | Latched<br>Drivers |                 | Saturated<br>Outputs | Internal<br>Protection | Part Number † |

| URCE DF          | RIVERS     |    |                 |                    |                 |                      |                        |               |

| -25              | 60         | 8  | _               | Х                  | _               | _                    | _                      | 5815          |

|                  | 60         | 10 | X               | X                  | Active Pull-Dow | n –                  | _                      | 5810-F        |

|                  | 60         | 12 | X               | X                  | -               | _                    | - 1                    | 5811          |

|                  | 60         | 20 | X               | ×                  | Active Pull-Dow | n –                  | -                      | 5812-F        |

|                  | 60         | 32 | X               | Х                  | Active Pull-Dow | n –                  | - 1                    | 5818-F        |

|                  | 65         | 8  | _               | _                  | _               | _                    | -                      | 6118-2        |

|                  | 80         | 8  | _               | Х                  | _               | _                    | _                      | 5815-1        |

|                  | 80         | 10 | X               | Х                  | Active Pull-Dow | n –                  | _                      | 5810-F-1      |

|                  | 80         | 20 | X               | Х                  | Active Pull-Dow | n –                  | - 1                    | 5812-F-1      |

|                  | 80         | 32 | X               | Х                  | Active Pull-Dow | n –                  | _                      | 5818-F-1      |

|                  | 85         | 6  | _               | _                  | _               | _                    | - 1                    | 6116          |

|                  | 85         | 8  | _               | _                  | _               | -                    | - 1                    | 6118          |

|                  | 115        | 8  | _               | _                  | _               | _                    | -                      | 6118-1        |

| -120             | -25        | 8  | _               | _                  | Х               | Х                    | _                      | 2585          |

|                  | 30         | 8  | _               | _                  | X               | Χ                    | - 1                    | 2985          |

|                  | 50         | 8  | X               | Χ                  | X               | X                    | -                      | 5895          |

| -350             | 35         | 8  | -               | _                  | X               | _                    | Х                      | 2987          |

|                  | 50         | 8  | _               | _                  | X               | _                    | -                      | 2981 and 2982 |

|                  | 50         | 8  | X               | Х                  | X               | _                    | _                      | 5891          |

|                  | -50        | 8  | _               | _                  | X               | _                    | - 1                    | 2580 and 2588 |

|                  | -80        | 8  | _               | _                  | X               | _                    | - }                    | 2588-1        |

|                  | 80         | 8  | _               | -                  | X               | _                    | -                      | 2983 and 2984 |

|                  | 80         | 8  | Х               | Х                  | X               | -                    | -                      | 5890          |

| -4000            | 60         | 4  | _               |                    | Х               | _                    | _                      | 2944          |

| URCE / S         | INK DRIVER | RS |                 |                    |                 |                      |                        |               |

| +350             | 7.0        | 2  | Voice           | Coil Motor I       | Drivor          | NMOS                 | Y                      | 3 0808        |

| ±350  | 7.0              | 2           | Voice-Coil Motor Driver                                                    | NMOS         | Х           | 8980 §                                     |

|-------|------------------|-------------|----------------------------------------------------------------------------|--------------|-------------|--------------------------------------------|

| ±500  | 6.0<br>6.0<br>40 | 2<br>2<br>4 | Voice-Coil Motor Driver<br>Voice-Coil Motor Driver<br>Dual Full Bridge X   | CMOS<br>CMOS | X<br>X<br>- | 8932-A §<br>8936 §<br>2993                 |

| ±750  | 45               | 4           | Dual PWM Bridge X                                                          | Х            | Х           | 2916                                       |

| ±800  | 16               | 2           | Voice-Coil Motor Driver                                                    | _            | Х           | 8958 §                                     |

| ±900  | 7.0<br>14        | 3<br>3      | 3-Ø Back-EMF Controller/Driver<br>3-Ø Back-EMF Controller/Driver           | DMOS<br>DMOS | X<br>X      | 8901 §<br>8902 §                           |

| ±1000 | 7.0<br>28        | 3<br>1      | 3-Ø Back-EMF Controller/Driver<br>Power Op Amp X                           | NMOS<br>-    | X<br>-      | 8980 §<br>3751                             |

| ±1500 | 45<br>45         | 4           | Dual PWM Full Bridge X<br>Dual PWM Full Bridge X                           | -            | X<br>X      | 2917<br>2918                               |

| ±2000 | 45<br>50<br>50   | 3<br>2<br>4 | 3-Ø Brushless Controller/Driver<br>PWM Full Bridge X<br>Dual Full Bridge X | -<br>-<br>-  | X<br>X<br>X | 2936 and 2936-120<br>2953 and 2954<br>2998 |

| ±3000 | 45               | 2           | PWM Control X                                                              | _            | _           | 2962                                       |

| ±3400 | 45               | 1           | PWM Control X                                                              | _            | Х           | 2961                                       |

| ±4000 | 14               | 3           | 3-Ø Brushless Controller/Driver                                            | DMOS         | Х           | 8925 §                                     |

<sup>\*</sup> Current is maximum specified test condition, voltage is maximum rating.

See specification for sustaining voltage limits or over-current protection voltage limits.

<sup>†</sup> Complete part number includes additional characters to indicate operating temperature range and package style.

<sup>‡</sup> Hall-Effect sensor. See Section 4.

<sup>§</sup> Mass Storage device. See Section 5.

### HIGH-VOLTAGE PERIPHERAL POWER AND DISPLAY DRIVERS

Section 3

#### IN ORDER OF 1) OUTPUT VOLTAGE, 1) OUTPUT CURRENT, 3) NUMBER OF DRIVERS

| Output Ratings* |      |    |                 |                    | Features       |                      |                        |               |

|-----------------|------|----|-----------------|--------------------|----------------|----------------------|------------------------|---------------|

| v               | mA   | #  | Serial<br>Input | Latched<br>Drivers | Diode<br>Clamp | Saturated<br>Outputs | Internal<br>Protection | Part Number † |

| 80              | -25  | 8  | _               | ×                  | _              | _                    | _                      | 5815-1        |

| j               | -25  | 10 | X               | X A                | ctive Pull-Do  | wn –                 | _                      | 5810-F-1      |

| l               | -25  | 20 | X               | X A                | ctive Pull-Do  | wn –                 | _                      | 5812-F-1      |

| l               | -25  | 32 | X               | X A                | ctive Pull-Do  | wn –                 | _                      | 5818-F-1      |

|                 | 300  | 2  |                 | _                  | _              | X                    | X                      | 5713          |

| 1               | 300  | 4  |                 | _                  | _              | X                    | X                      | 5703 and 5706 |

| }               | -350 | 8  | _               | _                  | Х              | _                    | -                      | 2983 and 2984 |

| 1               | 350  | 8  |                 | Х                  | Х              | _                    | _                      | 5822          |

| l               | 350  | 8  |                 | Х                  | Х              | X                    | -                      | 5842          |

| l               | -350 | 8  | X               | Х                  | Х              | _                    | -                      | 5890          |

| l               | 1500 | 2  |                 | -                  | _              | X                    | -                      | 2062          |

| }               | 1500 | 4  |                 | _                  | _              | X                    | _                      | 2065 and 2069 |

| ł               | 4000 | 4. | -               | -                  | Χ              | _                    | _                      | 2879          |

| -80             | -350 | 8  |                 |                    | Х              | -                    |                        | 2588-1        |

| 85              | -25  | 6  | _               | _                  | _              | _                    | _                      | 6116          |

|                 | -25  | 8  | _               | -                  | -              | _                    | _                      | 6118          |

| 95              | 350  | 7  | _               | _                  | Х              | _                    | _                      | 2023 and 2024 |

| 1               | 350  | 8  | _               | -                  | X              |                      | _                      | 2823          |

| 100             | 350  | 8  | ×               | X                  | _              | _                    |                        | 5823          |

|                 | 350  | 8  | X               | X                  | Х              | -                    | _                      | 5843          |

| 115             | -25  | 8  |                 |                    |                | _                    | _                      | 6118-1        |

| 150             | 250  | 7  | _               |                    | Х              | _                    | _                      | 7003          |

Current is maximum test condition; voltage is absolute maximum allowable.

Negative current is defined as coming out of (sourcing) the output.

<sup>†</sup> Complete part number includes additional characters to indicate operating temperature range and package style.

# **BIMOS SMART POWER INTERFACE DRIVERS**

Section 3

|                                            | Output I | Ratings * | Part Number † |

|--------------------------------------------|----------|-----------|---------------|

| SERIAL-INPUT LATCHED DRIVERS               |          |           |               |

| 8-Bit (saturated drivers)                  | -120 mA  | 50 V‡     | 5895          |

| 8-Bit `                                    | 350 mA   | 50 V      | 5821          |

| 8-Bit                                      | 350 mA   | 50 V‡     | 5841          |

| 8-Bit                                      | -350 mA  | 50 V‡     | 5891          |

| 8-Bit                                      | 350 mA   | 80 V      | 5822          |

| 8-Bit                                      | 350 mA   | 80 V‡     | 5842          |

| 8-Bit                                      | -350 mA  | 80 V‡     | 5890          |

| 8-Bit                                      | 350 mA   | 100 V     | 5823          |

| 8-Bit                                      | 350 mA   | 100 V‡    | 5843          |

| 9-Bit                                      | 1.6 A    | 50 V      | 5829          |

| 10-Bit (active pull-downs)                 | -25 mA   | 60 V      | 5810-F        |

| 10-Bit (active pull-downs)                 | -25 mA   | 80 V      | 5810-F-1      |

| 12-Bit                                     | -25 mA   | 60 V      | 5811          |

| 20-Bit (active pull-downs)                 | -25 mA   | 60 V      | 5812-F        |

| 20-Bit (active pull-downs)                 | -25 mA   | 80 V      | 5812-F-1      |

| 32-Bit (active pull-downs)                 | -25 mA   | 60 V      | 5818-F        |

| 32-Bit (active pull-downs)                 | -25 mA   | 80 V      | 5818-F-1      |

| 32-Bit                                     | 100 mA   | 30 V      | 5833          |

| 32-Bit                                     | 100 mA   | 40 V      | 5832          |

| ARALLEL-INPUT LATCHED DRIVERS              |          |           |               |

| 4-Bit                                      | 350 mA   | 50 V‡     | 5800          |

| 8-Bit                                      | -25 mA   | 60 V      | 5815          |

| 8-Bit                                      | -25 mA   | 80 V      | 5815-1        |

| 8-Bit                                      | 350 mA   | 50 V‡     | 5801          |

| Dual 8-Bit With Read Back                  | 25 mA    | 20 V‡     | 5881          |

| PECIAL-PURPOSE FUNCTIONS                   |          |           |               |

| Unipolar Stepper Motor Translator/Driver   | 1.25 A   | 50 V‡     | 5804          |

| Addressable 16-Line Latched Decoder/Driver | 350 mA   | 60 V‡     | 5816          |

| Addressable 28-Line Decoder/Driver         | 450 mA   | 30 V      | 5817          |

Current is maximum specified test condition, voltage is maximum rating. See specification for sustaining voltage limits.

Negative current is defined as coming out of (sourcing) the output.

<sup>†</sup> Complete part number includes additional characters to indicate operating temperature range and package style.

<sup>‡</sup> Internal transient-suppression diodes included for inductive-load protection.

### **MOTOR DRIVERS**

Sections 3, 4, and 5

| Function                                 | Output R       | latings * | Part Number †     | Detailed Info<br>Section |

|------------------------------------------|----------------|-----------|-------------------|--------------------------|

| NTEGRATED CIRCUITS FOR BRUSHLESS DC N    | MOTORS         |           |                   |                          |

| 3-Phase Controller/Drivers               | ±2.0 A         | 45 V      | 2936 and 2936-120 | 3                        |

| 2-Phase Hall-Effect Sensor/Controller    | 20 mA          | 25 V      | 3235              | 4                        |

| Hall-Effect Latched Sensors              | 10 mA          | 24 V      | 3175 and 3177     | 4                        |

| Hall-Effect Complementary Output Sensor  | 20 mA          | 25 V      | 3275              | 4                        |

| 2-Phase Hall-Effect Sensor/Driver        | 900 mA         | 14 V      | 3625              | 4                        |

| 2-Phase Hall-Effect Sensor/Driver        | 900 mA         | 26 V      | 3626              | 4                        |

| Hall-Effect Comp. Output Sensor/Driver   | 300 mA         | 60 V      | 5275              | 4                        |

| 3-Phase Back-EMF Controller/Driver       | ±900 mA        | 7 V       | 8901              | 5                        |

| 3-Phase Back-EMF Controller/Driver       | ±900 mA        | 14 V      | 8902              | 5                        |

| 3-Phase Controller/DMOS Driver           | ±4.0 A         | 14 V      | 8925              | 5                        |

| 3-Phase Back-EMF Controller/Driver       | ±1.0 A         | 7 V       | ₹ 8980            | 5                        |

| ULL-BRIDGE DRIVERS FOR DC AND BIPOLAR    | STEPPER MOTORS |           |                   |                          |

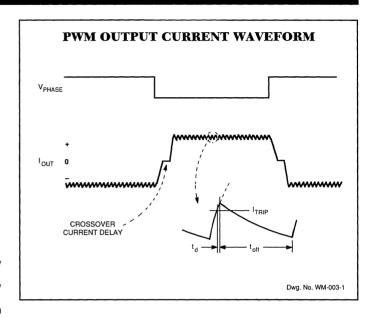

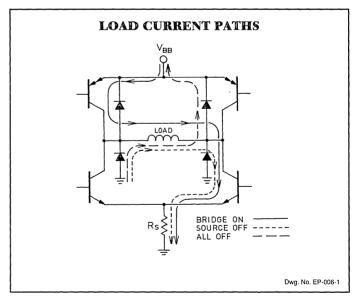

| PWM Current Controlled Dual Full Bridge  | ±750 mA        | 45 V      | 2916              | 3                        |

| PWM Current Controlled Dual Full Bridge  | ±1.5 A         | 45 V      | 2917              | 3                        |

| PWM Current Controlled Dual Full Bridge  | ±1.5 A         | 45 V      | 2918              | 3                        |

| PWM Current Controlled Full Bridges      | ±2.0 A         | 50 V      | 2953 and 2954     | 3                        |

| Dual Full Bridge                         | ±500 mA        | 40 V      | 2993              | 3                        |

| Dual Full Bridge                         | ±2.0 A         | 50 V      | 2998              | 3                        |

| THER MOTOR DRIVERS                       |                |           |                   |                          |

| Unipolar Stepper Motor Driver            | 1.8 A          | 50 V      | 2544              | 3                        |

| Linear Servo Motor Driver                | ±1.0 A         | 28 V      | 3751              | 3                        |

| Unipolar Stepper-Motor Translator/Driver | 1.25 A         | 50 V      | 5804              | 3                        |

| Voice-Coil Motor Driver                  | ±500 mA        | 6 V       | 8932-A            | 5                        |

| Voice-Coil Motor Driver                  | ±500 mA        | 6 V       | 8936              | 5                        |

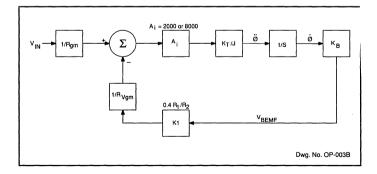

| Servo Controller System                  | _              | _         | 8951              | 5                        |

| Servo Loop Compensator                   | -              | -         | 8952              | 5                        |

| Voice-Coil Motor Driver                  | ±800 mA        | 16 V      | 8958              | 5                        |

| Voice-Coil Motor Driver                  | ±350 mA        | 7 V       | 8980              | 5                        |

Current is maximum specified test condition, voltage is maximum rating.

See specification for sustaining voltage limits or over-current protection voltage limits.

Negative current is defined as coming out of (sourcing) the output.

<sup>†</sup> Complete part number includes additional characters to indicate operating temperature range and package style.

#### HALL-EFFECT SENSORS

Section 4

#### UNIPOLAR HALL-EFFECT SWITCHES

| Switch Points (at<br>Max. Operate | T <sub>A</sub> = +25°C)<br>Min. Release | Max. Output<br>Ratings | Part Number * | Ext. Temp.<br>Available |

|-----------------------------------|-----------------------------------------|------------------------|---------------|-------------------------|

| 175 G                             | 25 G                                    | 2 x 25 mA†/25 V        | 3235          | _                       |

| 200 G                             | 50 G                                    | 25 mA/25 V             | 3140          | yes                     |

| 200 G                             | 50 G                                    | 900 mA/28 V            | 5140          |                         |

| 300 G                             | -25 G                                   | 24 V‡                  | 3055          | yes                     |

| 350 G                             | 50 G                                    | 25 mA/25 V             | 3120          | yes                     |

| 400 G                             | 140 G                                   | 25 mA/30 V             | 3122          | yes                     |

| 440 G                             | 180 G                                   | 25 mA/30 V             | 3123          | yes                     |

| 450 G                             | 30 G                                    | 25 mA/25 V             | 3113          |                         |

| 450 G                             | 125 G                                   | 25 mA/30 V             | 3121          | yes                     |

| Gear-Tooth Senso                  | ors, Zero Speed                         | 25 mA/28 V             | 3046/56/58    | yes                     |

| Gear-Tooth Senso                  | or, AC Coupled                          | 25 mA/24 V             | 3059          | yes                     |

<sup>\*</sup> Complete part number includes additional characters to indicate operating temperature range and package style.

#### **BIPOLAR HALL-EFFECT SWITCHES**

| Switch Points (at Max. Operate | t T <sub>A</sub> = +25°C)<br>Min. Release | Max. Output<br>Ratings | Part Number * | Ext. Temp.<br>Available |

|--------------------------------|-------------------------------------------|------------------------|---------------|-------------------------|

| +75 G                          | -75 G                                     | 25 mA/25 V             | 3133          | yes                     |

| +95 G                          | -95 G                                     | 25 mA/25 V             | 3132          | yes                     |

| +150 G                         | -150 G                                    | 25 mA/25 V             | 3130          | yes                     |

#### **BIPOLAR HALL-EFFECT LATCHES**

| Switch Points (at | t T <sub>A</sub> = +25°C) | Max. Output      |               | Ext. Temp. |

|-------------------|---------------------------|------------------|---------------|------------|

| Min. Operate      | Max. Operate              | Ratings          | Part Number * | Available  |

| ±50 G             | ±150 G                    | . 15 mA/18 V     | 3177          | _          |

| ±50 G             | ±150 G                    | 25 mA/30 V       | 3187          | yes        |

| ±25 G             | ±170 G                    | 15 mA/18 V       | 3175          | _          |

| ±80 G             | ±180 G                    | 25 mA/30 V       | 3188          | yes        |

| ±50 G             | ±230 G                    | 25 mA/30 V       | 3189          | yes        |

| ±25 G             | ±250 G                    | 2 x 50 mA/25 V†  | 3275          | · -        |

| ±25 G             | ±250 G                    | 2 x 500 mA/30 V† | 5275          | -          |

| ±170 G            | ±270 G                    | 25 mA/30 V       | 3185          | yes        |

| ±70 G             | ±330 G                    | 25 mA/30 V       | 3186          | yes        |

<sup>\*</sup> Complete part number includes additional characters to indicate operating temperature range and package style.

#### **LINEAR HALL-EFFECT SENSORS**

| Description                 | Part Number * | Ext. Temp.<br>Available |

|-----------------------------|---------------|-------------------------|

| Typical output 0.7 mV/gauss | 3501          | -                       |

| Typical output 1.3 mV/gauss | 3503          | _                       |

| Typical output 2.5 mV/gauss | 3506/07       | yes                     |

<sup>\*</sup> Complete part number includes additional characters to indicate operating temperature range and package style.

<sup>†</sup> Output 1 switches on south pole, output 2 switches on north pole.

<sup>‡</sup> Multiplexed two-wire sensor; after proper address, power/signal bus current indicates magnetic field condition.

<sup>†</sup> Complementary outputs for 2-phase unipolar brushless dc motor control.

See also, 2429 fluid detector and 5348 smoke detector, Section 6.

# DEVICES FOR MASS STORAGE APPLICATIONS

Section 5

| Part Number* | Description                                                                        |

|--------------|------------------------------------------------------------------------------------|

| 8901         | 5 V 3-Phase Brushless DC Motor Controller/Driver with Back-EMF Sensing             |

| 8902         | 5 V and 12 V 3-Phase Brushless DC Motor Controller/Driver with Back-EMF Sensing    |

| 8920         | Dual Schottky Diode                                                                |

| 8925         | 3-Phase Motor Controller/Driver with Linear Current Control and Power DMOS Outputs |

| 8932-A       | 6 V, 600 mA Voice Coil Motor Driver                                                |

| 8936         | 6 V, 600 mA Voice Coil Motor Driver                                                |

| 8951         | Servo Controller System                                                            |

| 8952         | Servo Loop Compensator                                                             |

| 8958         | 16 V, 250 mA Voice Coil Motor Driver                                               |

| 8980         | Spindle & Voice-Coil Actuation Manager/Driver                                      |

<sup>\*</sup> Complete part number includes additional characters to indicate operating temperature range and package style.

# **DEVICES FOR PRINTER APPLICATIONS**

Section 3

| Part Number* | Description                                                     |

|--------------|-----------------------------------------------------------------|

| 2916         | Dual 45 V, 750 mA Full-Bridge PWM Stepper Motor Driver          |

| 2917         | Dual 45 V, 1.5 A Full-Bridge PWM Stepper Motor Driver           |

| 2918         | Dual 45 V, 1.5 A Full-Bridge PWM Stepper Motor Driver           |

| 2961         | 45 V, 3.4 A Solenoid Printhead Driver                           |

| 2962         | Dual 45 V, 3 A Solenoid Printhead Driver                        |

| 5817         | Addressable 30 V, 450 mA 28-Line Ink-Jet Printer Decoder/Driver |

| 5829         | Serial-In 50 V, 1.6 A 9-Wire Solenoid Printhead Driver          |

<sup>\*</sup> Complete part number includes additional characters to indicate operating temperature range and package style.

### AUTOMOTIVE, SIGNAL-PROCESSING, AND CONSUMER ICS

#### **EXTENDED TEMPERATURE DEVICES SUITABLE FOR AUTOMOTIVE APPLICATIONS**

| Part<br>Number *         | Function                                            | Detailed Info<br>Section |

|--------------------------|-----------------------------------------------------|--------------------------|

| 2001, 2003, 2004,        |                                                     |                          |

| 2013, and 2023           | High-Voltage, High-Current Darlington Arrays        | 3                        |

| 2065 and 2068            | 1.5 A Darlington Switches                           | 3                        |

| 2429                     | Fluid (Low-Coolant) Detector                        | 6                        |

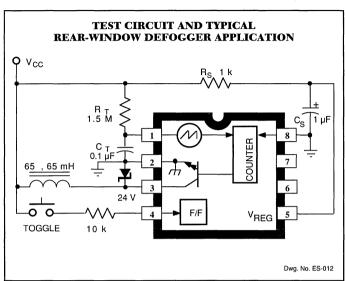

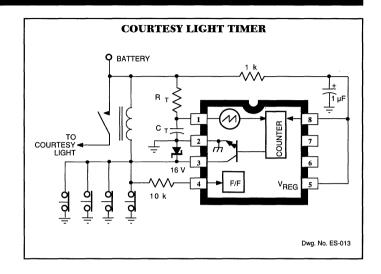

| 2436                     | Countdown Power Timer (Rear-Window Defogger)        | 6                        |

| 2454 and 2455            | Lamp Monitors                                       | 6                        |

| 2460                     | Electronic Spark Timing                             | 6                        |

| 2543, 2547, & 2549       | Protected Quad Power Drivers                        | 3                        |

| 2596                     | 8-Channel Saturated Sink Driver                     | 3                        |

| 2801, 2803, 2804, & 2823 | High-Voltage, High-Current Darlington Arrays        | 3                        |

| 2916                     | Dual Full-Bridge PWM Motor Driver                   | 3                        |

| 2943                     | High-Current Half-Bridge Motor Driver               | 3                        |

| 2981 thru 2984           | 8-Channel Source Drivers                            | 3                        |

| 3046, 3056, & 3058       | Hall-Effect Gear-Tooth Sensors - Zero Speed         | 4                        |

| 3059                     | Hall-Effect Gear-Tooth Sensor - AC Coupled          | 4                        |

| 3120                     | Hall-Effect Switch                                  | 4                        |

| 3121, 3122, & 3123       | Hall-Effect Switches                                | 1 4                      |

| 3130                     | Hall-Effect Switch                                  | 4                        |

| 3132 and 3133            | Ultra-Sensitive Bipolar Hall-Effect Switches        | 4                        |

| 3140                     | Hall-Effect Switch                                  | 4                        |

| 3141, 3142, & 3143       | Sensitive Hall-Effect Switches                      | 4                        |

| 3185 thru 3189           | Hall-Effect Latches                                 | 4                        |

| 3506 and 3507            | Ratiometric, Linear Hall-Effect Sensors             | 4                        |

| 3828                     | FM Stereo Decoder                                   | 6                        |

| 3841                     | AM Signal Processor                                 | 6                        |

| 3844                     | Dual-Conversion AM Receiver                         | 6                        |

| 3845 and 3846            | AM Noise Blankers                                   | 6                        |

| 3848                     | Dual-Conversion AM Receiver                         | 6                        |

| 4000                     | Medium-Power Darlington Array                       | 7                        |

| 5140                     | Protected PowerHall Sensor - Lamp/Solenoid Driver   | 4                        |

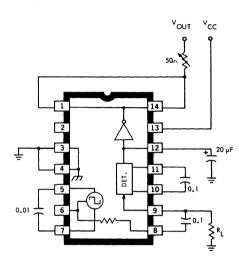

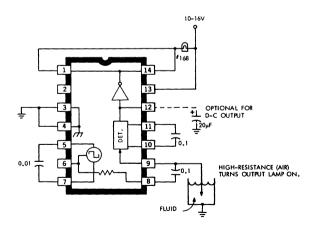

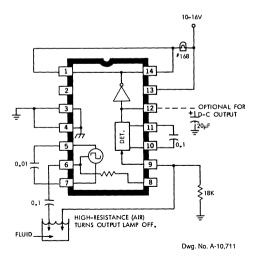

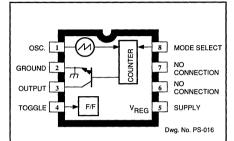

| 5616                     | LCD Automotive Clock - Programmable                 | 6                        |