intel

**i**SBC Applications Handbook

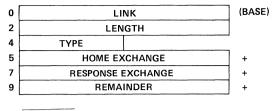

**i**SBC Applications Handbook

# iSBC™ APPLICATIONS HANDBOOK

**SEPTEMBER 1981**

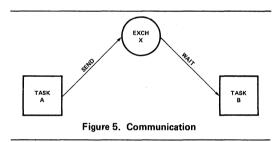

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9 (a) (9). Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of intel Corporation.

The following are trademarks of Intel Corporation and may only be used to identify Intel products:

| BXP    | Intelevision    | MULTIBUS      |

|--------|-----------------|---------------|

| CREDIT | Intellec        | MULTIMODULE   |

| i      | iSBC            | Plug-A-Bubble |

| ICE    | iSBX            | PROMPT        |

| ICS    | Library Manager | Promware      |

| im     | MCS             | RMX           |

| Insite | Megachassis     | UPI           |

| Intel  | Micromainframe  | $\mu$ Scope   |

|        | Micromap        | System 2000   |

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation

Literature Department SV3-3

3065 Bowers Avenue

Santa Clara, CA 95051

© INTEL CORPORATION, 1981 AFN-01300C-1

## **PREFACE**

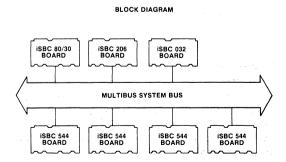

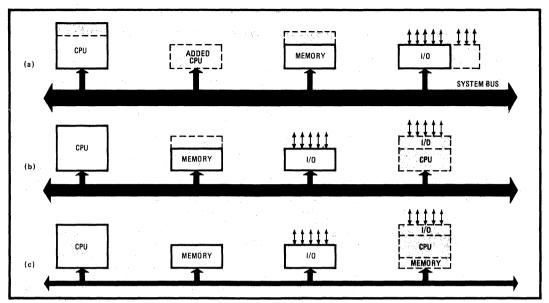

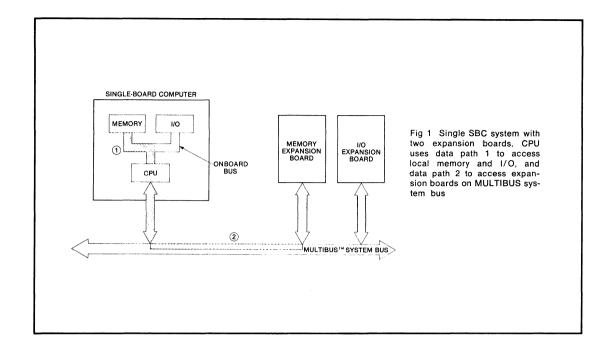

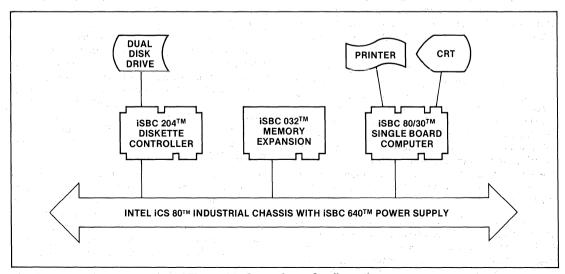

Since Intel introduced the iSBC 80/10 Single Board Computer in early 1976, the family of Intel OEM Microcomputer Systems has grown rapidly. Original equipment manufacturers and volume end-users alike have responded to the concept originated by Intel of having all the functions of a computer — central processing unit, memory, input-output and system expansion capability — present on one printed circuit board.

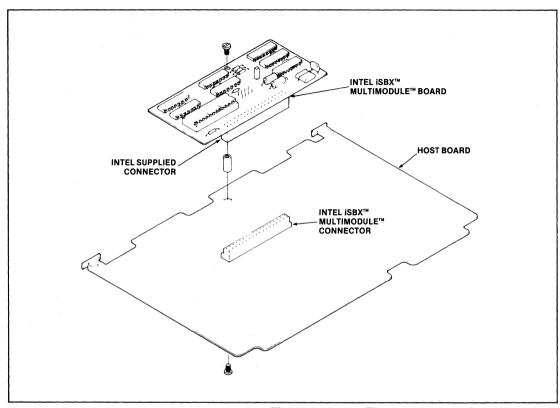

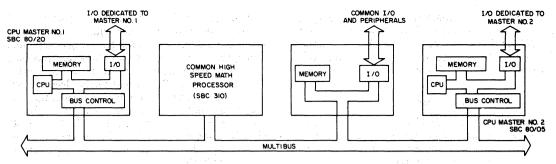

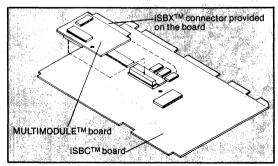

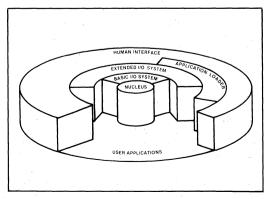

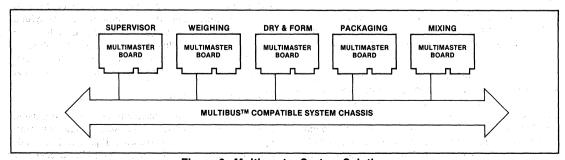

The capabilities of a single board computer have been enhanced by the creation of the industry-standard MULTIBUS system bus. System expansion boards have been introduced for memory, serial I/O and parallel I/O expansion, as well as analog I/O, DMA controllers and peripheral controllers. A unique feature of the MULTIBUS architecture, however, is its capability to support multiple single board computers. This capability permits sophisticated multiprocessing configurations using standard off-the-shelf 8-bit and 16-bit single board computers. The introduction of the iSBX MULTIMODULE expansion boards has revolutionized the concept of the single board computer. Now iSBC host boards may be custom configured with iSBX expansion boards based on the I/O requirements of the application. This capability provides lower cost, higher performance single board solutions. Powerful software tools like the iRMX 80 and iRMX 88 Real-Time Executives and the iRMX 86 Operating System are key members of the iSBC product family. They provide users with the tools for quick implementations of simple or complex systems. iCS product line provides chassis and signal conditioning/termination strips as well as board level products which were developed specifically for industrial users.

This application manual is divided into three sections: iSBC Hardware, iSBC Software and iCS Products. It contains all of the current application notes, reliability reports, magazine articles and professional journal reprints on the products of the Intel iSBC product family. We have compiled all of this information into a single publication for your convenience. Please contact us with your questions, comments, and suggestions on how we may provide you with useful information on our products.

INTEL CORPORATION

OEM Microcomputer Systems Applications Engineering Hillsboro, Oregon 97123

# **TABLE OF CONTENTS**

| ISBC H          | ISBC HARDWARE                                                                               |             |         | SOFTWARE (con't.)                                                               |  |  |

|-----------------|---------------------------------------------------------------------------------------------|-------------|---------|---------------------------------------------------------------------------------|--|--|

| AP-26           | iSBC 80/10A-SYSTEM 80/10<br>Single Board Computer Applica-                                  | 10          | AP-86   | Using the iRMX 86 Operating System 2-73                                         |  |  |

| AP-28A<br>AP-43 | Intel MULTIBUS Interfacing                                                                  | 1-3<br>1-45 | AP-88   | Multiprocessing Extensions for the RMX/80 Real-Time Executive                   |  |  |

| AP-43           | Using the iSBC 957 Execution<br>Vehicle for Executing 8086<br>Program Code                  | 1-79        | AP-109  | Using Intel Single Board<br>Computers for Serial Distributed                    |  |  |

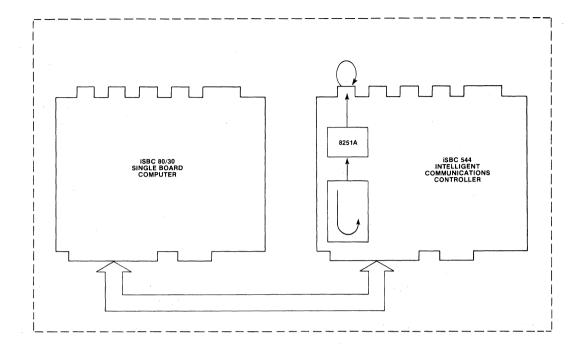

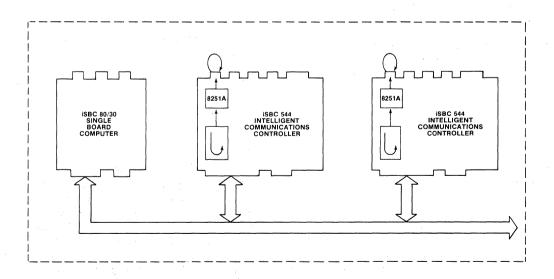

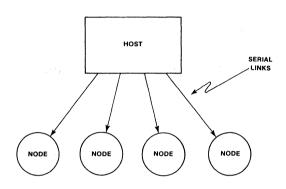

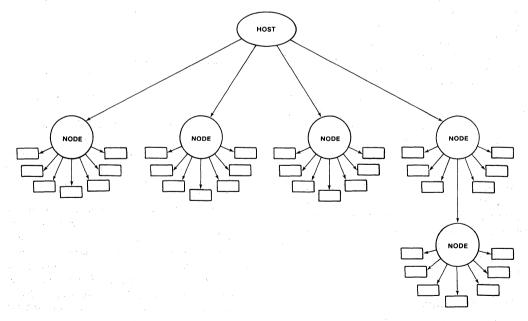

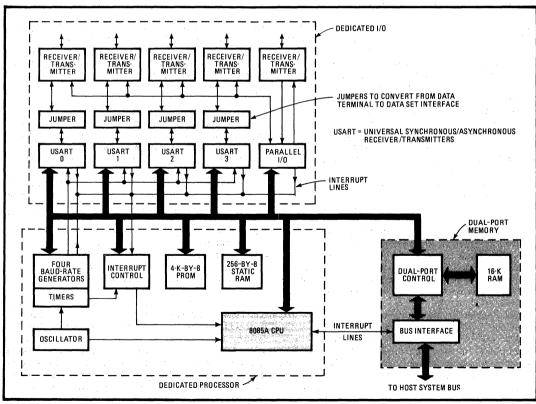

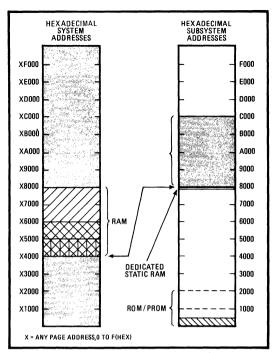

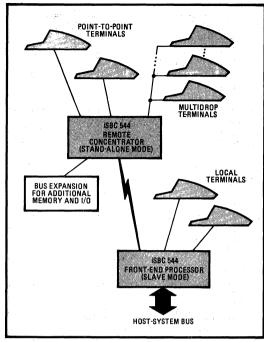

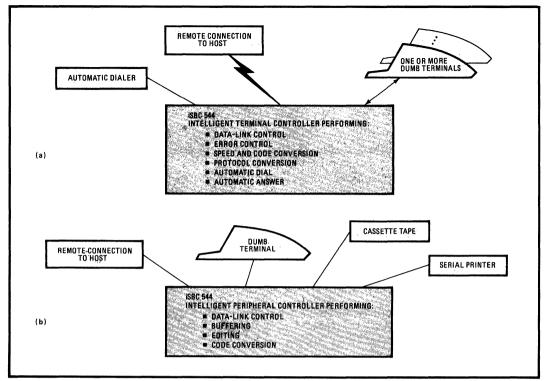

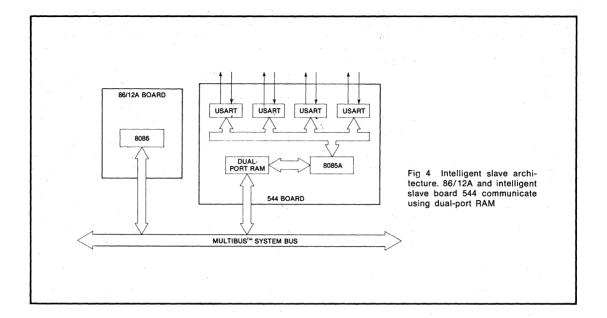

| AP-53           | Using the iSBC 544 Intelligent Communications Controller                                    | 1-111       | AP-110  | Processing Links 2-173 Using the iRMX 86 Operating                              |  |  |

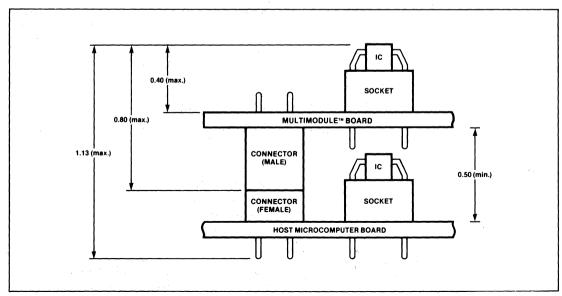

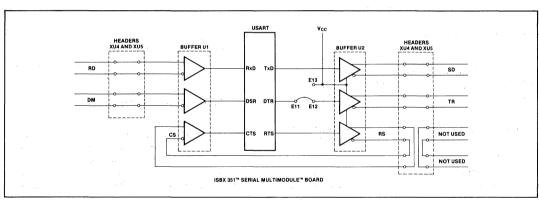

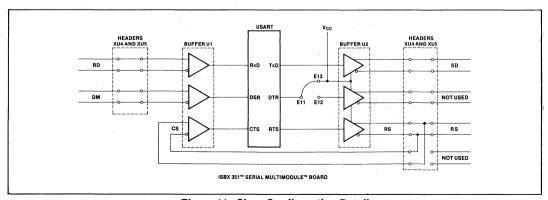

| AP-96           | Designing iSBX MULTIMODULE Boards                                                           | 1-175       |         | System on iAPX 86 Component Designs 2-243                                       |  |  |

| AR-48           | Reduce Your $\mu$ C-Based System Design Time by Using Single                                |             | AR-41   | An Integral Real-Time Executive for Microcomputers 2-303                        |  |  |

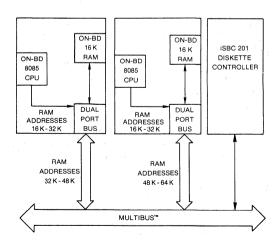

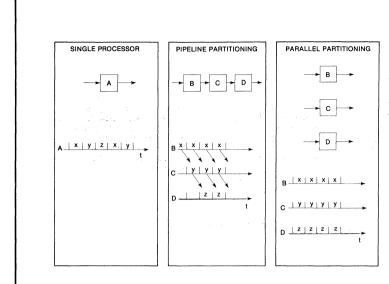

| AR-55           | Board Microcomputers  Design Motivations for Multiple Processor Microcomputer               |             | AR-124  | Introducing the RMX/86 Real-<br>Time, Multitasking, 16-Bit<br>Operating System  |  |  |

| AR-65           | Triple-Bus Architecture on a                                                                |             | AR-125  | Modular Multitasking Executive<br>Cuts Cost of 16-Bit OS Design 2-315           |  |  |

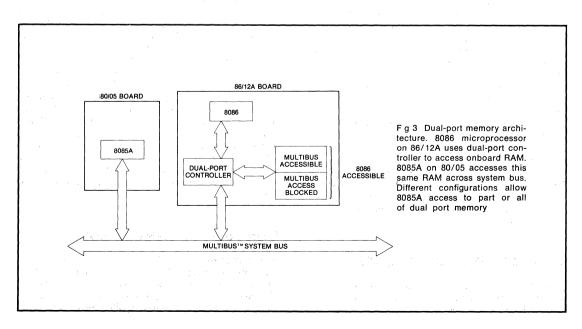

| AR-69           | Single Board Microcomputer  Dual-Port RAM Hikes Throughput in Input/Output Controller Board |             |         | A Small-Scale Operating System Foundation for Microprocessor Applications 2-321 |  |  |

| AR-72           | 16-Bit Single Board Computer<br>Maintains 8-Bit Family Ties                                 | 1-237       | AR-172  | Multitasking Executive Speeds 16-Bit Micros 2-329                               |  |  |

| AR-122          | A New Family of MULTIMODULE                                                                 |             | iCS PRO | ODUCTS                                                                          |  |  |

|                 | Boards Extends the Solutions Provided by Intel's Single Board Computers                     | 1-245       | AP-52   | Using Intel's Industrial Control<br>Series in Control Applications 3-3          |  |  |

| AR-123          | Special Function Modules Ride on Computer Board                                             |             | AP-60   | Closed Loop Control Using the iSBC 569/941 Intelligent Digital Processors 3-61  |  |  |

| AR-133          | Multiprocessing System Mixes 8- and 16-Bit Microcomputers                                   | 1-257       | AR-91   | Designing and Assembling<br>Microcomputer Systems Grows                         |  |  |

| ISBC S          | OFTWARE                                                                                     |             |         | Easier 3-123                                                                    |  |  |

| AP-33           | RMX/80 Real-Time Multitasking Executive                                                     | 2-3         | DOCUM   | IENTATION                                                                       |  |  |

| AP-47           | Using FORTRAN-80 for iSBC                                                                   |             |         | Related Intel Publications 4-3                                                  |  |  |

|                 | Applications                                                                                | 2-33        |         | Technical Literature List 4-5                                                   |  |  |

# *iSBC*<sup>™</sup> *Hardware*

1

SP Single Board Complifer Special Compliter

# iSBC 80/10A-SYSTEM 80/10 Single Board Computer Applications

## Contents

| INTRODUCTION              | 1-5 |

|---------------------------|-----|

| OVERVIEW                  | 1-5 |

| SBC CONFIGURATION OPTIONS | 1-7 |

| Serial I/O Options        | 1-7 |

| Parallel I/O Options      |     |

| Bus Interfacing           | 1-8 |

| APPLICATIONS 1            | -10 |

| Instrumentation           | -10 |

| Communication             | -15 |

| Process Control           | -23 |

| I/O Device Controller     | -27 |

| CONCLUSION1               | -31 |

| APPENDIX A — iSBC 80/10A  |     |

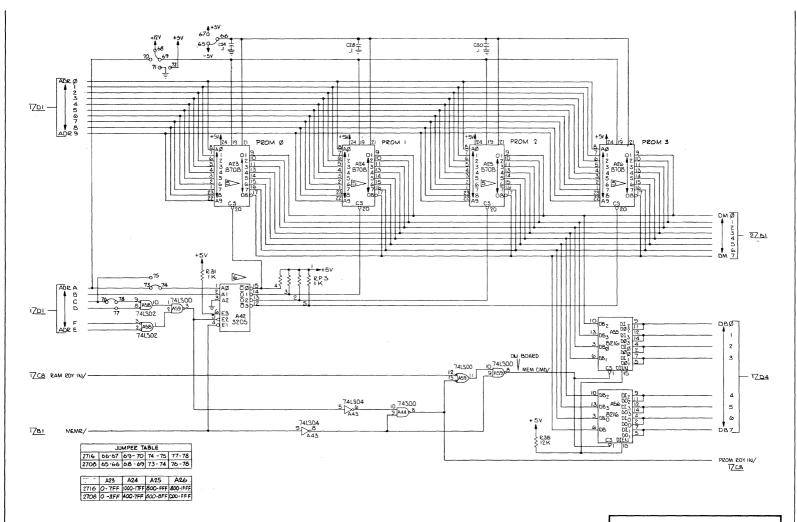

| SCHEMATICS 1              | -33 |

#### INTRODUCTION

The recent entry of the single board computer into the broad field of electronic applications is substantiating the billing as a "super component". Single board computers provide a solution to several problems that have not been solved by the use of conventional computers: cost, size, and design specialization.

Many potential microcomputer applications have been overlooked because of the design tasks required to build a microcomputer system. These tasks traditionally include interfacing of the system clock, read/write memory, I/O ports and drivers, serial communications interface, bus control logic and drivers. Intel's iSBC 80/10A enables the design engineer to concentrate on the application of microcomputers, rather than on implementation details.

This application note begins with an overview of the Intel® iSBC 80/10A. Readers who are familiar with the iSBC 80/10A may choose to skip to the applications section, which describes the following typical iSBC 80/10A applications:

- The iSBC 80/10A used for instrumentation control of a Fluke 8375 Digital Multimeter.

- The iSBC 80/10A used as a SCADA Terminal in a communication application.

- The iSBC 80/10A used for temperature monitoring in a process control application.

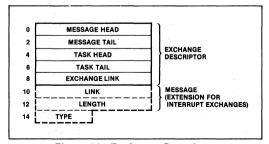

- The iSBC 80/10A used as an interrupt driven device controller for a Centronics printer.

Each example shows the user program and hardware required for the application. The program listings are interspersed with the text describing the application. Both 8080 Macro Assembly Language and Intel's PL/M-80 are used in the examples.

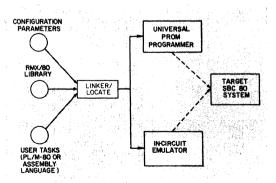

The software was developed on an Intel® Microcomputer Development System (MDS). The MDS provided the tools necessary to edit, assemble or compile, link and locate the application software. Hardware development was facilitated by the use of Intel's In-Circuit Emulator (ICE 80). For further information regarding the Microcomputer Development System, the reader is referred to the publications listed at the beginning of this application note.

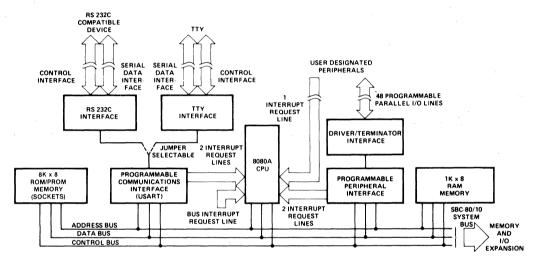

#### **OVERVIEW**

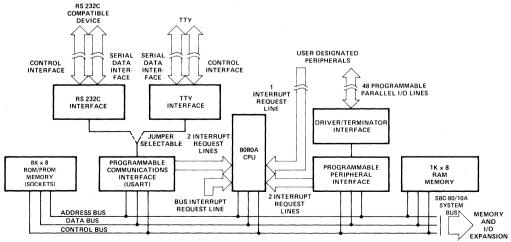

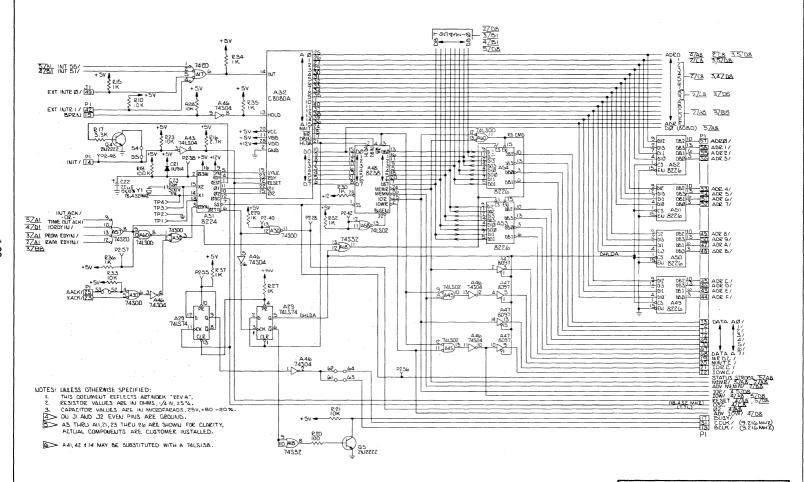

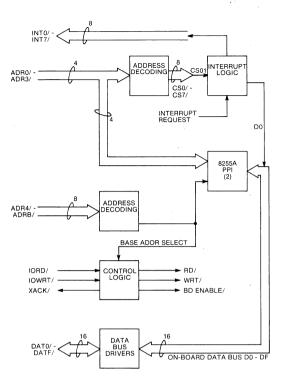

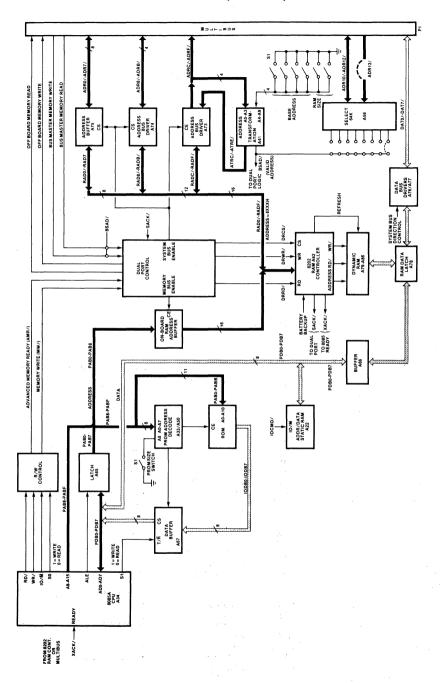

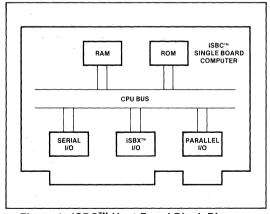

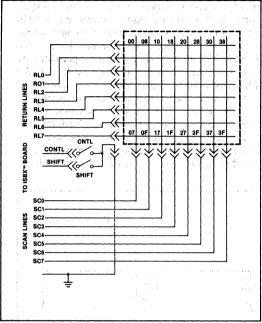

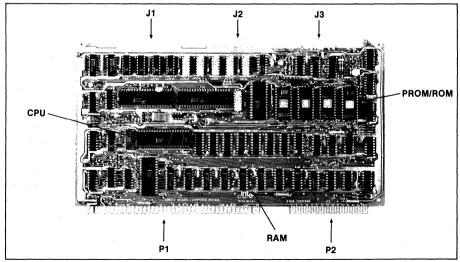

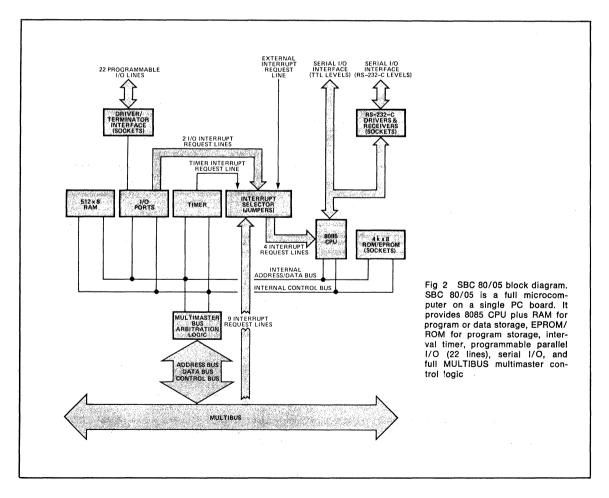

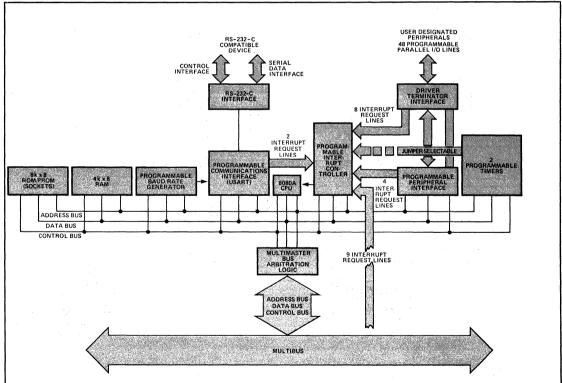

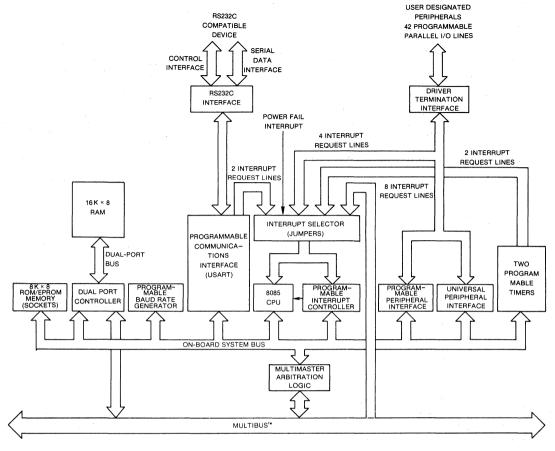

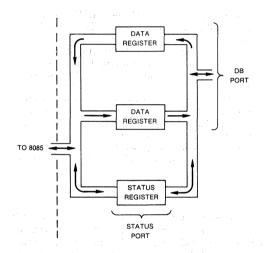

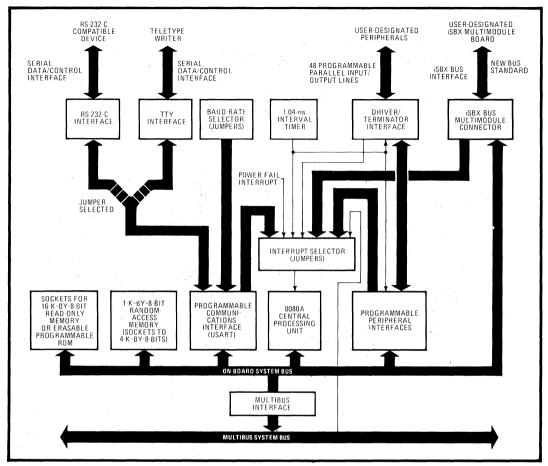

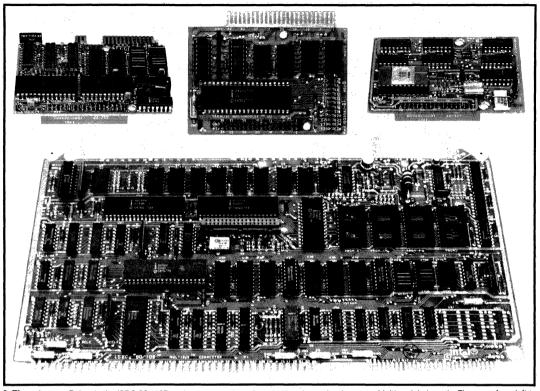

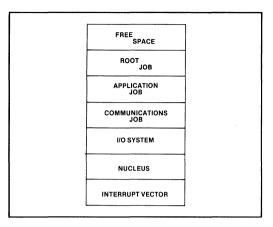

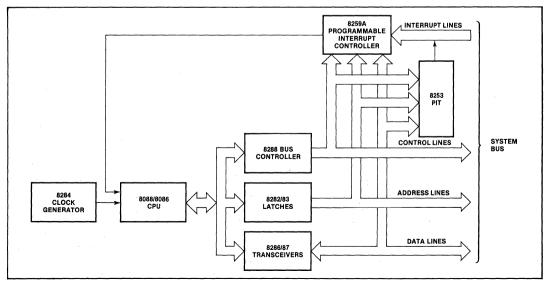

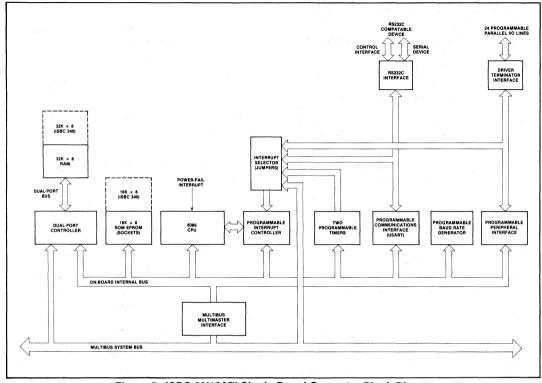

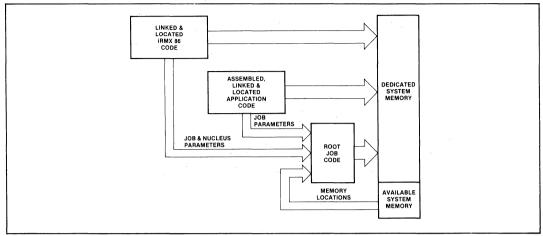

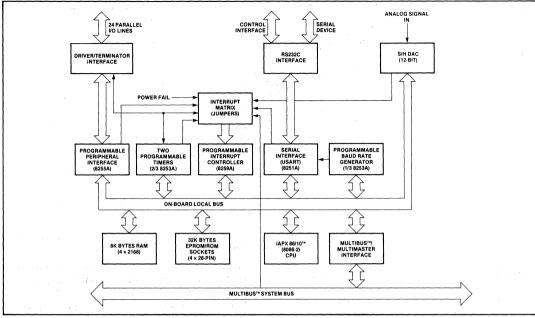

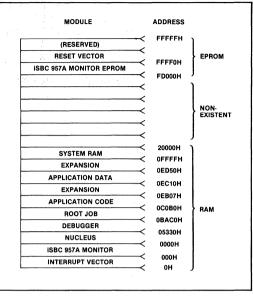

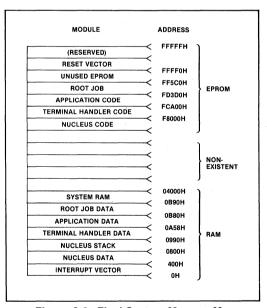

The iSBC 80/10A is a member of Intel's complete line of OEM computer systems which take full advantage of Intel's LSI technology to provide economical, self-contained computer based solutions for OEM applications. The iSBC 80/10A is a complete computer system on a single 6.75-by-12 inch printed circuit card. A block diagram of the iSBC 80/10A is shown in Figure 1.

Intel's powerful 8-bit n-channel MOS 8080A CPU, fabricated on a single LSI chip, is the central processor for the iSBC 80/10A. The 8080A contains six 8-bit general purpose registers and an accumulator. The six general purpose registers may be addressed individually or in pairs, providing both single and double precision operators.

1. Interrupts originating from the Programmable Communications Interface and Programmable Peripheral Interface are jumper selectable.

Figure 1. iSBC 80/10A Block Diagram

The 8080A has a 16-bit program counter which allows direct addressing of up to 64K bytes of memory. An external stack, located within any portion of read/write memory, may be used as a last in/first out stack to store the contents of the program counter, flags, accumulator and all of the six general purpose registers. A 16-bit stack pointer addresses the external stack. This provides subroutine nesting that is bounded only by memory size.

The iSBC 80/10A contains 1K bytes of read/ write memory using Intel's low power static RAM. All on board RAM read and write operations are performed at maximum processor speed. Four sockets for up to 8K bytes of non-volatile readonly memory are provided on the board. Readonly memory may be added in 1K byte increments (up to 4K total) using Intel<sup>®</sup> 8708 erasable and electrically reprogrammable ROMs (EPROMs) or Intel 8308 masked ROMs. Optionally, if more than 4K bytes are required, read only memory may be added in 2K byte increments (up to 8K total) using Intel® 2716 EPROMs or 2316E masked ROMs. All on-board ROM or EPROM read operations are performed at maximum processor speed.

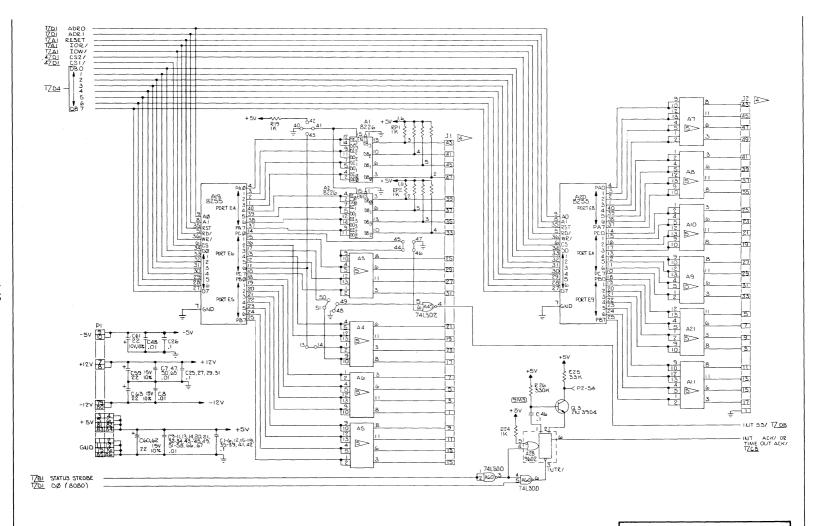

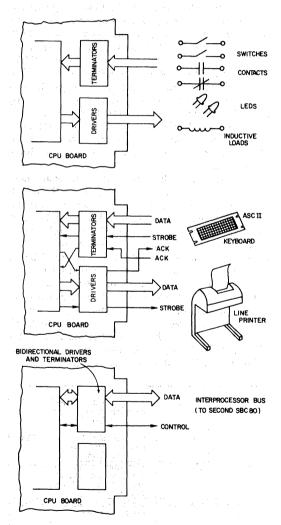

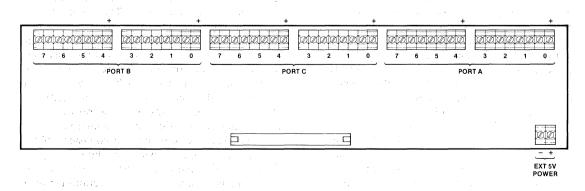

The iSBC 80/10A contains 48 programmable parallel I/O lines implemented using two Intel® 8255 Programmable Peripheral Interfaces. The system software is used to configure the I/O lines in any combination of unidirectional input/output, and bidirectional ports indicated in Table I. Therefore, the I/O interface may be customized to meet specific peripheral requirements. To support the large number of possible I/O configurations, sockets are provided for interchangeable I/O line drivers and terminators. Hence, the I/O interface

provides the appropriate combination of optional line drivers and terminators to allow the required sink current, polarity, and drive/termination characteristics for each application. The 48 programmable I/O lines and signal ground lines are brought out to two 50-pin edge connectors that mate with flat, round, or woven cable.

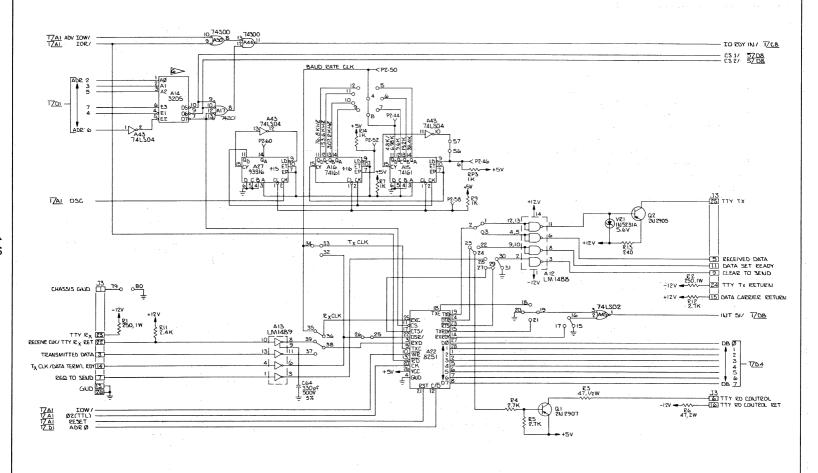

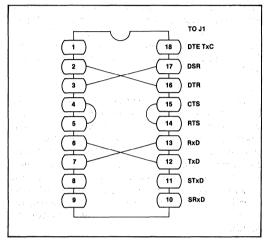

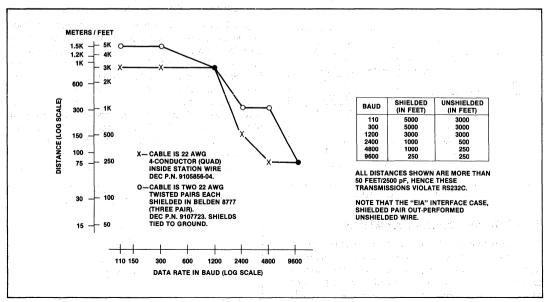

A programmable communications interface using Intel's 8251 Universal Synchronous/Asynchronous Receiver/Transmitter (USART) is contained on the iSBC 80/10A. A jumper selectable baud rate generator provides the 8251 with all common communication frequencies. The 8251 can be programmed by the user's system software to select the desired asynchronous or synchronous serial data transmission technique (including IBM Bisync). The mode of operation (synchronous or asynchronous), data format, control character format, parity, and asynchronous transmission rate are all under program control. The 8251 provides full duplex, double buffered transmission and receive capability. Parity, overrun, and framing error detection circuits are all incorporated in the 8251. The inclusion of jumper selectable TTY or EIA RS232C compatible interfaces on the board, in conjunction with the 8251, provide a direct interface to teletypes, CRTs, asynchronous and synchronous modems, and other RS232C compatible devices. The RS232C or TTY command lines, serial data lines, and signal ground lines are brought out to a 25-pin edge connector that mates with RS232C compatible flat, round, or woven

Interrupt requests may originate from six sources. Two from the 8255's, two from the 8251 and two from user designated peripheral devices.

TABLE 1 INPUT/OUTPUT PORT MODES OF OPERATION

|      |              |           |                   | MODE O  | F OPERATION       |               |         |

|------|--------------|-----------|-------------------|---------|-------------------|---------------|---------|

|      |              |           | UNIDIRECTIONAL    |         |                   |               |         |

| PORT | NO. OF LINES | INPUT     |                   | OUTPUT  |                   | BIDIRECTIONAL | CONTROL |

| FORT | NO. OF LINES | UNLATCHED | LATCHED & STROBED | LATCHED | LATCHED & STROBED | BIDIRECTIONAL | CONTROL |

| 1    | 8            | ×         | X                 | Х       | ×                 | , , <b>x</b>  |         |

| 2    | 8            | Х         | X                 | X       | X                 |               |         |

| 3    | 8            | X         |                   | . X     |                   |               | X1      |

| 4    | 8            | X         |                   | - X     |                   |               |         |

| 5    | 8            | . X       |                   | X       |                   |               |         |

| 6    | 4            | X         |                   | Х       |                   | 1. 1          |         |

|      | 4            | X.        |                   | X       |                   |               |         |

Note: Port 3 must be used as a control port when either Port 1 or Port 2 are used as a latched and strobed input or a latched and strobed output or Port 1 is used as a bidirectional port.

The 8255's can generate interrupts when a byte of information is ready to be transferred to the CPU (i.e., input buffer full) or a byte of information has been transferred to a peripheral device (i.e., output buffer is empty).

The 8251 can generate interrupts when a character is ready to be transferred to the CPU (i.e., receive channel buffer is full) or a character is ready to be transmitted (i.e., transmit channel data buffer is empty).

The user designated peripheral devices can generate two interrupts: one via the system bus and the other via the I/O edge connector.

The two interrupts from the 8255's and the two interrupts from the 8251 are all individually maskable under program control. The six interrupt request lines share a single CPU interrupt level. When an interrupt request is recognized, a RE-START 7 instruction is generated. The processor responds by suspending program execution and making a subroutine call to a user defined interrupt service routine originating at location 38 (Hexadecimal).

iSBC 80/10A memory and I/O capacity may be increased by adding standard Intel memory and I/O boards. Modular expandable backplanes and card cages, each with a four-board capacity, are available to support multi-board systems.

The development cycle of iSBC 80/10A based products may be significantly reduced using the Intellec Microcomputer Development System. The resident macro-assembler, PL/M-80 compiler, text editor, and system monitor greatly simplify the design, development, and debug of user designed iSBC 80/10A system software. A diskette-based system allows programs to be loaded, assembled, edited, and executed faster than using conventional paper tape, card, or cassette peripherals. A unique In-Circuit Emulator (ICE 80) provides the capability of developing and debugging software directly on the iSBC 80/10A.

#### **iSBC CONFIGURATION OPTIONS**

The iSBC 80/10 provides the user with a powerful and flexible I/O capability for both parallel and serial transfers. This section discusses the user programmable and jumper-selectable options, and bus interfacing.

#### SERIAL I/O OPTIONS

The serial I/O interface, using Intel's 8251 USART, provides a serial data communications channel that can be programmed to operate with most of the

current serial data transmission protocols. There are three general areas of serial I/O options:

- 1. choice of interface type, RS232C or current loop,

- 2. baud rate and program-selectable mode options,

- 3. choice of an interrupt mechanism.

The user has the choice, through jumper connections, of configuring the serial I/O logic to present either an RS232C or a 20 mA current loop interface to an external device. If an RS232C interface is used, the 8251 can assume the role of a "data set" or a "data processing terminal". This enables the serial interface to be connected to different devices such as modems and computer terminals.

There are two factors which enter into the choice of baud rate. They are the actual clock frequency used to drive the transmit/receive clocks on the 8251 and the baud rate factor selected by a programmable mode instruction control word output by the processor to the 8251. The baud rate factor is used to effectively divide the 8251 transmit and receive clocks by 1, 16 or 64. During normal operation a factor of 16 is selected for asynchronous transmissions from 9.6K to 300 baud. A factor of 64 must be used to achieve a baud rate of 110. The baud rate factor is only applicable to asynchronous transmission, as all synchronous transmission is done with an implied factor of one.

Before beginning serial I/O operations, the 8251 must be program-initialized to support the desired mode of operation. The CPU initializes the 8251 by issuing a set of control bytes to the USART device. These control words specify:

- synchronous or asynchronous operation

- baud rate factor

- character length

- number of stop bits

- even/odd parity

- parity/no parity

Refer to the iSBC 80/10 and iSBC 80/10A Single Board Computer Hardware Reference Manual or the "8251 Application Note" for details on the control words used to direct the operation of the 8251.

The serial I/O logic can be configured with different forms of interrupt request mechanisms. By connecting a jumper, the user can allow the 8251's Receiver Ready output to generate an interrupt request. The Receiver Ready output goes high whenever the Receiver Enable bit of the command

1-7 AFN-01931A

word has been set and the 8251 contains a character that is ready to be input to the CPU. The user can also choose to have the 8251's Transmitter Ready or Transmitter Empty output activate the interrupt request. The Transmitter Empty goes high when the 8251 has no characters to transmit. Transmitter Ready is high when the 8251 is ready to accept a character from the CPU. Both Transmitter Empty and Transmitter Ready are enabled by setting the Transmit Enable bit of the command word. Upon receiving an interrupt, the program can determine the actual condition which is responsible for the interrupt by reading the status of the 8251 device.

#### PARALLEL I/O OPTIONS

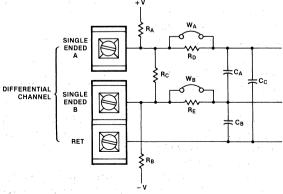

The parallel I/O interface consists of six 8-bit I/O ports implemented with two Intel 8255 Programmable Peripheral Interface devices. Eight lines already have a bidirectional driver and termination network permanently installed. The remaining 40 lines are uncommitted. Sockets are provided for the installation of active driver networks or passive termination networks as required to meet the specific needs of the user system.

The primary considerations in determining how to use each of the six I/O ports are:

- 1. choice of operating mode,

- 2. direction of data flow (input, output or bidirectional),

- 3. selection of interrupt mechanism,

- 4. choice of driver/termination networks for the port's data path.

Operating Modes. There are three basic operating modes that can be selected by the system software. The modes of operation will be described here in general terms, leaving it to the reader to obtain details from the iSBC 80/10 and iSBC 80/10A Single Board Computer Hardware Reference Manual or the "8255 Application Note."

Mode 0 is a basic input/output functional configuration which provides simple input and output operations. No "handshaking" is required, data is simply written to or read from a specified port. The outputs are latched and the inputs are unlatched.

Mode 1 is a strobed input/output functional configuration which provides a means for transferring I/O data to or from a specified port in conjunction with strobes or handshaking signals. The outputs are latched and are accompanied by

an output control line which indicates that the processor has loaded the output port with a data byte. The input data is latched when accompanied by its externally operated control signal.

Mode 2 is a strobed bidirectional bus input/output functional configuration which provides a means for communicating with a peripheral device or structure on a single 8-bit bus for both transmitting and receiving data. Handshaking signals are provided to maintain proper bus flow discipline in a manner similar to mode 1.

Data Flow Direction. In addition to the choice of operating mode, the user may also specify the direction of data flow, input or output from the 8255's. At the time of RESET, the 8255's are configured into the input mode until altered by a control word directed to the control word register. When an output mode control word is received, all of the data bits are set to the low output state.

Interrupt Mechanism. When the 8255 is programmed to operate in mode 1 or mode 2, control signals are provided that can be used as interrupt request inputs to the CPU. The interrupt request signals, generated from one of the ports (port C), can be inhibited or enabled by setting or resetting the associated interrupt enable flip-flop, using the bit set/reset function of port C. This function allows the programmer to mask the interrupts from specific I/O devices without affecting any other device in the interrupt structure.

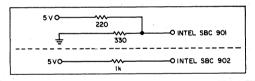

Driver/Termination Networks. Depending on the direction of data flow, the user will select the appropriate TTL line drivers and Intel terminators that are compatible with the I/O driver/terminator sockets on the iSBC 80/10A. The list of suitable line drivers includes those with inverting, non-inverting, and open collector characteristics. There are two types of terminators: a 220-ohm/330-ohm divider or a 1K ohm pull-up.

### BUS INTERFACING

The system bus interface logic consists of three general groups of circuitry:

- gates that accept the various bus control signals, the interrupt request lines, and the ready indications, and then apply these signals to the CPU logic elements,

- 2. the system bus drivers,

- 3. the failsafe circuitry which generates an acknowledgment during interrupt sequences and during those cycles in which an ac-

knowledgment is not returned because a non-existent device was inadvertently addressed.

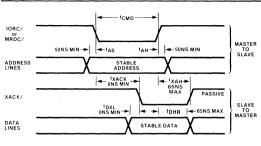

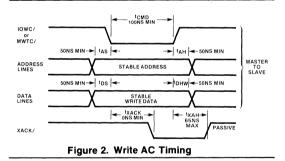

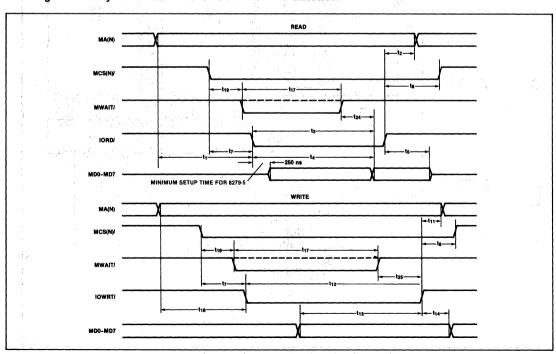

Bus Interface Signals. The following paragraphs describe portions of the system bus interfacing logic relevant to interfacing a user device to the iSBC 80/10A. (Note: Whenever a signal is activelow, its mnemonic is followed by a slash; for example, MRDC/ means that the level on that line will be low when the memory read command is true.)

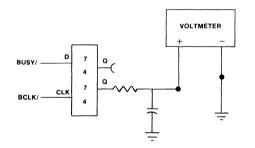

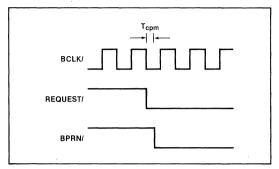

- BCLK/ Bus clock; used to synchronize bus control circuits on all master modules. BCLK/ has a frequency of 9.216 MHz. BCLK/ may be slowed, stopped or single stepped, if desired.

- INIT/ Initialization signal; resets the entire system to a known internal state.

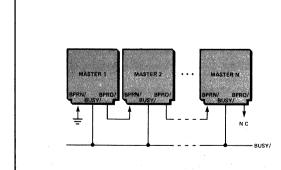

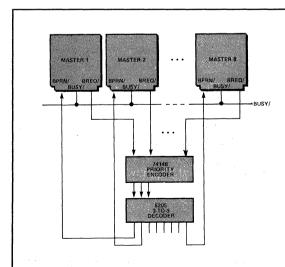

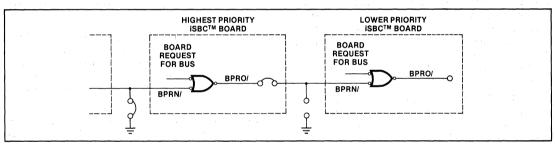

- BPRN Bus priority input signal; indicates to the iSBC 80/10A that a higher priority master module is requesting use of the system bus. BPRN suspends the processing activity and drivers of the iSBC 80/10A until the signal goes low.

- BUSY/ Bus busy signal; indicates that the bus is currently in use. BUSY/ prevents all other master modules from gaining control of the bus. BUSY/ is driven by the HLDA/ output from the iSBC 80/10A in response to a BPRN input. It indicates that the bus is available.

- MRDC/ Memory read command; indicates that the address of a memory location has been placed on the system address lines and specifies that the contents of the addressed location are to be read and placed on the system data bus.

- MWTC/ Memory write command; indicates that the address of a memory location has been placed on the system address lines and that a data word has been placed on the system data bus. MWTC/ specifies that the data word is to be written into the addressed memory location.

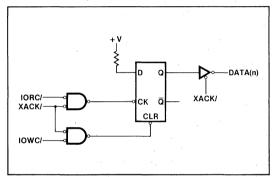

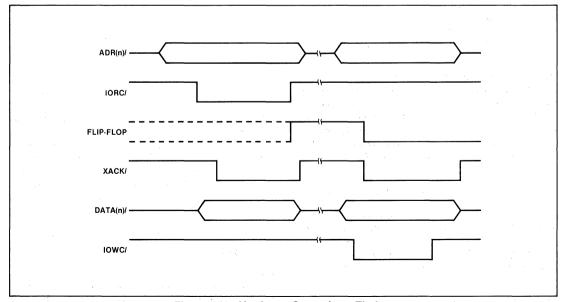

- IORC/ I/O read command; indicates that the address of an input port has been placed on the system address bus and that the data at that input port is to be read and placed on the system data bus.

- IOWC/ I/O write command; indicates that the address of an output port has been placed on the system address bus and that the contents

- of the system data bus are to be output to the addressed port.

- XACK/ Transfer acknowledge signal; the required response of an external memory location or I/O port which indicates that the specified read/write operation has been completed (that is, data has been placed on, or accepted from, the system data bus lines).

- AACK/ An advance acknowledge, in response to a memory read or write command, that allows the memory to complete the specified operation without requiring the CPU to wait.

- CCLK/ Constant clock; provides a clock signal of constant frequency (9.216 MHz) for use by optional memory and I/O expansion boards. The same signal is used to drive both CCLK/ and BCLK/.

- INTR1/ Externally generated interrupt request.

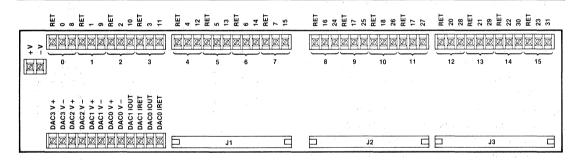

- ADR0/-ADRF/ 16 Address lines; used to transmit the address of the memory location or I/O port to be accessed. ADRF/ is the most significant bit.

- DAT0/-DAT7/ Bidirectional data lines; used to transmit/receive information to/from a memory location or I/O port. DAT7/ is the most significant bit.

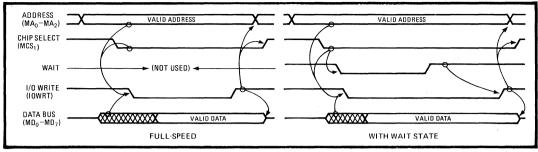

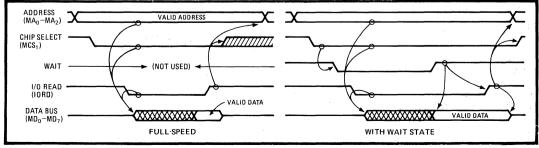

Bus Acknowledges. Further distinction between transfer acknowledge (XACK/) and advance acknowledge (AACK/) is required. All external memory and I/O transfer requests must return XACK/ to the iSBC 80/10A (even if AACK/ is also returned). XACK/ indicates that data has been placed on (read command) or accepted from (write command) the system data bus lines. AACK/ is an advance acknowledge in response to a memory or I/O port command. It has been provided because the 8080A samples the ready line before valid data is required on the bus. If this condition is properly anticipated, AACK/ can be returned before the data is actually read, thus allowing an earlier operation to be completed. AACK/ should be used only with a thorough understanding of the additional information provided in the iSBC 80/10 and iSBC 80/10A Single Board Computer Hardware Reference Manual, DMA Transfers, An external device can make DMA transfers to or from RAM expansion boards. The transfer is coordinated with the iSBC 80/10A by means of two bus signals: bus priority input (BPRN) and bus busy (BUSY/). The first step in making a DMA transfer is to obtain control of the system bus. This is

1-9 AFN-01931A

achieved by asserting BRPN to the iSBC 80/10A and then waiting until the iSBC 80/10A returns BUSY/, indicating that it has relinquished control of the system bus. When this step is completed the external device may proceed with its DMA transfers until it is finished. At that time BPRN should be removed to allow the iSBC 80/10A to regain control of the system bus. It should be noted that the iSBC 80/10A is placed in a hold state when it does not have control of the system bus.

#### APPLICATIONS

The iSBC 80/10A may be applied to a wide variety of applications. Specific applications in four areas are presented in this application note. They are presented to illustrate a broad spectrum of single board computer capabilities and to demonstrate the use of various system features.

#### INSTRUMENTATION

Microprocessors have been used in instrumentation for many tasks ranging from handling simple interface functions to control of the analog to digital conversion process. The use of a single board computer can further serve in the application of instruments themselves to laboratory or process control environments. It is quite often necessary in these applications to control instrumentation remotely. A number of rather expensive minicomputer-controlled solutions now exist on the market as automatic test equipment (ATE) systems. The iSBC 80/10A presents itself as a cost effective solution in situations where the larger ATE systems are beyond economic justification.

The iSBC 80/10A can be the sole CPU element in the system, providing instrumentation control and computational capability; or it can supplement a larger host CPU by handling distributed processing requirements.

#### **Instrumentation Control Application Example**

Most instruments such as DVMs, counters, data loggers, synthesizers, etc., have optional data output units (DOUs) and/or remote control units (RCUs). It is particularly time consuming to interface each instrument's DOU/RCU with custom-digital logic. Until the recent IEEE-488 interface standard, there was little in common from one interface to the next. The parallel I/O lines of the iSBC 80/10A provide a common interface element that can be adapted to a majority of the DOUs and RCUs available today by means of software.

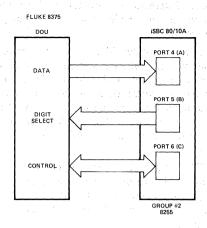

Figure 2. Interface Block Diagram

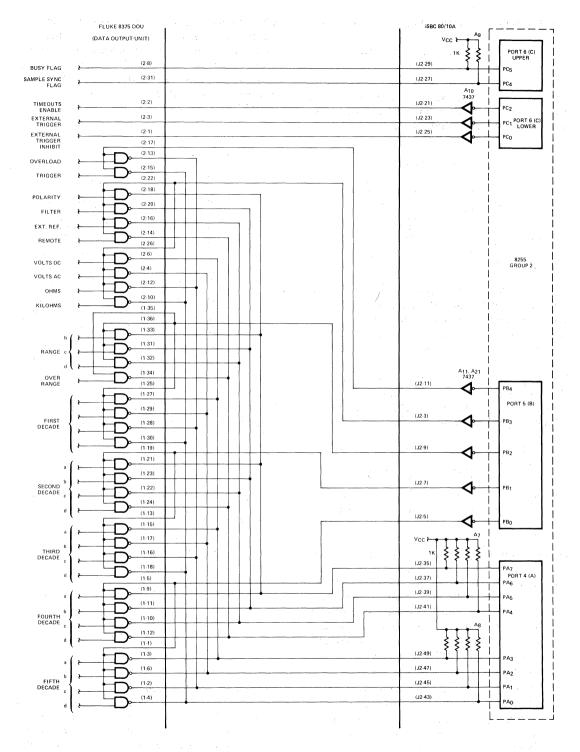

This instrumentation control application shows how the iSBC 80/10A has been used to control and read the data from the data output unit (DOU) of a Fluke 8375 Digital Multimeter.

Interfacing the iSBC 80/10A to the Fluke 8375 DOU has been accomplished through the use of three parallel I/O ports shown in Figure 2. An 8-bit port has been used to read input data from the Fluke 8375 DOU. Another 8-bit port has been used to control the multiplexing of data from the DOU to the iSBC 80/10A. And, an 8-bit port has been used to provide the required control and monitoring of the following DOU functions: busy flag, sample sync flag, timeout enable, external trigger and trigger inhibit.

The following listing contains a complete program to provide the necessary interface control functions as well as an exercise program. The program listing is interspersed with text that is used to clarify the elements of the program.

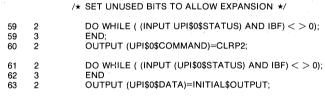

0 : INSTRUMENTATION CONTROL APPLICATION

2 : FLUKE 8375 DIGITAL MULTIMETER

4 : DATA OUTPUT UNIT (DOU) CONTROLLER

6 : T

The CSEG directs the ISIS-II 8080 Assembler to generate a relocatable code segment. Relocatable code can later be placed at any memory address by Intel's LOCATE program. This lets you write your program without worrying about the application's final memory configuration.

10; 11: CSEG 12; 13 Equate Table. The following table is used to give symbolic names to the binary I/O port addresses. The names used later in the program increase readability.

```

14

15 : EQUATE TABLE

16 : EQUATE TABLE

16 : EQUATE TABLE

17 : EQUATE TABLE

18 CWR EQU OEBH ; 8255 #2 COWTROL WORD REGISTER

18 CWR EQU OEBH ; DECADE PAIR DATA INPUT PORT

20 STB EQU OEBH ; STROBE QUTPUT PORT

21 FLG EQU OEBH ; FLAG INPUT PORT

22 TRG EQU OEBH ; TRIGGER OUTPUT PORT

22 TRG EQU OEBH ; TRIGGER OUTPUT PORT

```

The exercise program uses some of the subroutines provided in the iSBC 80/10A System Monitor PROMs. The addresses of the subroutines are included in the equate table.

```

25 ;

26 ;

27 GETCH BQU 0220H ; GET CONSOLE INPUT, MASK OFF PARITY 28 CO BQU 01B8H ; CONSOLE OUTPUT SQ CROUT BQU 01F3H ; PAINT CAP<CLP>

30 MMOUT BQU 02C2H ; DISPLAY BYTE IN ACCUM 33 ;

```

The use of the iSBC 80/10A parallel I/O ports requires that the mode of operation be defined for each port. This is typically done by an initialization subroutine executed when the iSBC 80/10A is powered up or reset.

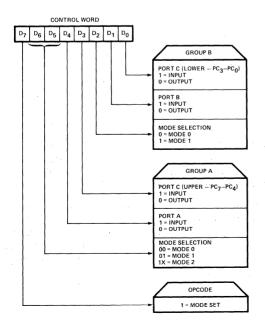

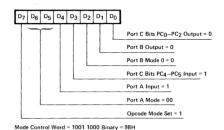

8255 Control Word. When the opcode field (bit 7) of a control word directed to an 8255 is equal to one, the control word is interpreted as a mode definition control word. The mode definition control word format is shown below:

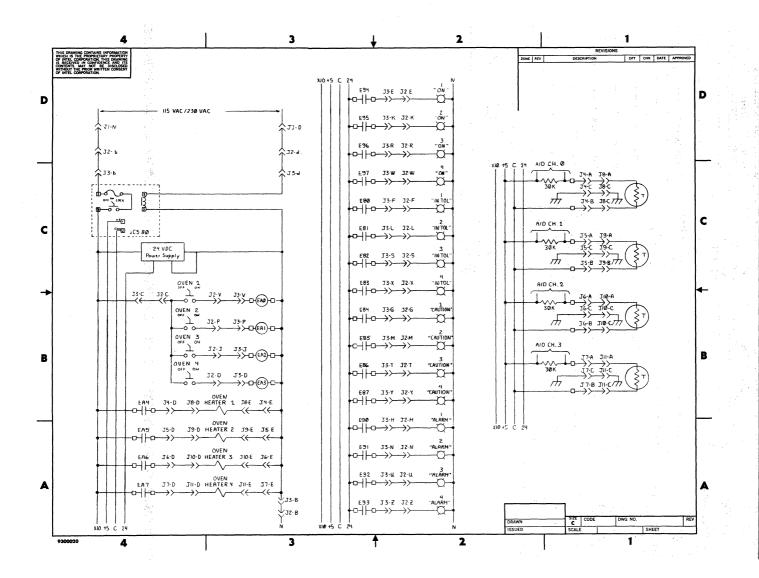

Observing the schematic for the iSBC 80/10A — Fluke 8375 DOU (Figure 3), it can be seen that the 8255 #2 should be configured through the use of the mode control word as:

```

Port 4 (A) Mode 0 Input

Port 5 (B) Mode 0 Output

Port 6 (C) Bits PC2—PC0 Output

Port 6 (C) Bits PC5—PC4 Input

```

The following mode control word is used:

33 34 ; \*\*\* 8255 #2 INITIALIZATION SUBROUTINE 36 ; \*\*\* 8255 #2 INITIALIZATION SUBROUTINE 37 INIT: 38 MVI A,10011000B ; LD MODE CONTROL MORD 39 OUT CWR ; OUTPUT TO 8255#2 CNTL WD REG 40 ;

This coding loads the mode control word into the 8255 #2 control word register. Additional initialization code is required to set the strobe and trigger output ports to an inactive state. The schematic shows that inverting drivers have been used for both the strobes and the trigger. When a command is issued to place port 5 (B) into the output mode, bits PB7-PB0 are set to the low output state. Because the low outputs are then inverted and used as strobes to the Fluke 8375, they must then be disabled. The initialization subroutine concludes by disabling the strobes and trigger. The strobes are signals to the DOU which enable its drivers to send data to the iSBC 80/10A. The trigger is a signal to the DOU that the Fluke 8375 should take a reading.

```

42

43;

44 4WI A,0FFH; LD MASK TO:

45 OUT STB; DISABLE STROBES

46 OUT TRG; DISABLE TRIGGER

47 RET

48;

49

```

External Trigger Control. Two subroutines are implemented to enable and disable the external trigger mode of the instrument. These subroutines use the bit set/reset capability of the 8255 to independently set or reset three control lines of the Fluke 8375 DOU.

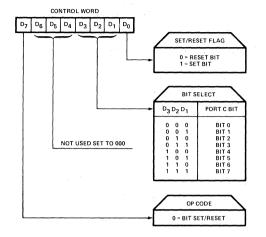

When the opcode field (bit 7) of an 8255 control word equals zero, the control word is a port 6 (C) bit set/reset command word.

The bit set/reset control word format is shown below:

The following example demonstrates how the port 6 (C) bit set/reset control word is constructed to disable the Fluke 8375 external trigger. Note from the schematic (Figure 3) that port 6 (C) bit 0 controls the inhibit external trigger line.

Subroutines to enable and disable the timeouts are written in an analogous fashion. The timeout enable line is controlled by port 6 (C) bit 2.

| 67<br>68 |            |         |                    |     |        |                       |

|----------|------------|---------|--------------------|-----|--------|-----------------------|

| 69       | ; ***      | ENABLE  | TIMEOUTS SUBROUTIN | E · | ***    |                       |

| 70<br>71 | ;<br>EPOS: |         |                    |     |        |                       |

| 72       |            | MVI     | A,00000101B        | ;   | LD SET | BIT 2 CONTROL WORD    |

| 73       |            | OUT     | CWR                | ;   | OUTPUT | TO 8255#2 CNTL WD REG |

| 74       |            | RET     |                    |     |        |                       |

| 75       | ;          |         |                    |     |        |                       |

|          | ; ***      | DISABLE | TIMEOUTS SUBROUTI  | ΝE  | ***    |                       |

|          | i          |         |                    |     |        |                       |

|          | ; ***      |         | TIMEOUTS SUBROUTI  | NE  | ***    |                       |

| 79         | MVI | A,00000100B | ; LD RESET BIT 2 CONTROL WORD, |

|------------|-----|-------------|--------------------------------|

| 80         |     | CWR         | ; OUTPUT TO 8255#2 CNTL WD REG |

| 81<br>82 ; | RET |             |                                |

Obtaining Readings. The Fluke 8375 DOU allows readings to be taken in one of two modes. The first, a triggered mode, assumes that the external triggering has not been inhibited and requires the positive edge of a pulse with a minimum width of 1 microsecond on the trigger input. Setting and resetting the port 6 (C) bit 1 produces the 8375 external trigger. After a reading is triggered the 8375 busy flag is tested until the not busy state is reached. At that time the reading that was triggered can be read by the iSBC 80/10A. The last statement in this routine jumps to TKDATA which reads the data from the DOU and then executes the return.

| 84<br>85<br>86             | ; ***      | SUBROUT                 | INE TO TAKE EXTE                  | RNALLY TRIGGERED READING ***                                                                                |

|----------------------------|------------|-------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------|

| 87<br>88                   | ;<br>TRGR: |                         |                                   |                                                                                                             |

| 89                         |            | MVI                     | A,00000010B                       | ; LD RESET BIT 1 CONTROL WORD                                                                               |

| 90                         |            | OUT                     | CWR                               | OUTPUT TO 8255#2 CNTL WD REG                                                                                |

| . 91<br>92                 |            | INR                     | A<br>CWR                          | ; MODIFY CONTROL WORD TO SET BIT 1<br>; OUTPUT TO 8255#2 CNTL WD REG                                        |

| 93                         | TWT:       |                         |                                   |                                                                                                             |

| 94<br>95<br>96<br>97<br>98 |            | IN<br>ANI<br>JNZ<br>JMP | FLG<br>00100000B<br>TWT<br>FKDATA | ; INPUT THE BUSY FLAG<br>; TEST PORT C BIT 5<br>; LOOP UNTIL NOT BUSY<br>; GO READ DATA FROM DOU AND RETURN |

| 90                         | ,          |                         |                                   |                                                                                                             |

The second method for reading the Fluke 8375 is to rely on the sample rate set from the front panel controls and to wait until a full transition of the busy flag is observed. This guarantees that a previous reading is not mistakenly interpreted as a new reading.

Notice that the loops beginning at NXTWT in the above program segment and at TWT in the previous program segment are identical. This suggests the possibility of some obvious code optimization that is omitted here for the sake of clarity.

There is one subroutine remaining to complete full utilization of the Fluke 8375 DOU capabilities. It is the subroutine to take data from the 8375 DOU. The schematic (Figure 3) shows that port 5 (B) bits PB4—PB0 are used to enable the DOU drivers. Data from the DOU includes:

- 5 decades of digits

- encoded range and overrange

- function: Volts DC, Volts AC, Ohms, Kilohms

- modifiers: Filter, Ext. Ref., Remote

- overload

- trigger

The function of this subroutine is to read five bytes of data from the 8375 DOU and place them in a RAM buffer on the iSBC 80/10A.

```

*** SUBROUTINE TO TAKE DATA FROM 8375 DOU ***

119 TKDATA:

H, RDBUF

MVT

A.OEFH

SETUP FIRST STROBE

122 TKO:

123

124

SAVE CURRENT STROBE

STROBE DECADE PAIR

OUT

SŤB

125

126

127

DATIN

READ DATA

MOV

PLACE DATA INTO SBC 80/10 RAM

INCREMENT BUFFER POINTER

A.B

RESTORE STROBE

128

MOV

RRC

JC

OUT

; ROTATE TO NEXT STROBE POSITION

; LOOP UNTIL BIT O STROBE DONE

; DISABLE ALL STROBES

```

This completes the software required to service the Fluke 8375 DOU. The following code consists of a routine to display the data from the interface on the console output device and a short executive program to allow exercising of the driver subroutines.

The display subroutine takes 5 bytes of data from the RAM buffer in which the reading has been stored and prints them, 2 ASCII characters per 8-bit byte, on the console.

```

: *** SUBROUTINE TO DISPLAY READING BUFFER ON CONSOLE ***

137 ; *** SU

138 ;

139 DISPLAY:

H.RDBUE

: LD BUFFER POINTER

141

MVT

D,5

: INITIALIZE COUNTER

142 DISPO:

LD NEXT BYTE FROM BUFFER

CALL SBC 80/10 MONITOR SUBROUTINE

A,M

NMOUT

CALL

TO DISPLAY ACCUMULATOR CONTENTS

INCREMENT BUFFER POINTER

145

INX

DCR

DECREMENT COUNTER

DISPO

148

JNZ

: LOOP FOR 5 DISPLAY BYTES

```

Operator Interface. The short executive program provides a tool for the purposes of exercising the 8375 DOU driver subroutines. The executive begins by calling the initialization subroutine and then continues on to prompt the operator with a '>' on the console. At that point the operator may enter one of the following characters, causing the program to execute the specified subroutine:

|   | SUBR    | DESCRIPTION                 |

|---|---------|-----------------------------|

| T | ETRIG   | Enable external trigger     |

| I | DTRIG   | Disables external trigger   |

| E | EPOS    | Enable programmed timeouts  |

| D | DPOS    | Disable programmed timeouts |

| N | NXTRD   | Next reading                |

| S | TRGR    | Trigger and get a reading   |

| X | DISPLAY | Display reading buffer      |

After the operator has entered a command character, the program obtains the address of the subroutine to be executed and proceeds to set up a return address on the stack. This technique allows a load program counter instruction (PCHL) to be used to enter the subroutine and a return instruction (RET) to resume execution of the executive.

```

152

153

154

*** SIMPLE EXECUTIVE EXERCISE PROGRAM ***

155;

156 START:

157

158

SP.STACK

SETUP STACK POINTER

CALL

INIT

; INITIALIZE THE SBC 80/10 8255#2

EXEC:

EXEC ENTRY POINT - PRINT <CR><LF>

CROUT

EXEC ENTRY POINT - PRINT (CHX)CLF)

C LOADED WITH PROMPT CHARACTER

CONSOLE OUTPUT

GET CMND CHAR, MASK OFF PARITY

PRINT THE CHARACTER ON THE CONSOLE

PUT CHARACTER BACK INTO THE ACCUM

161

162

IVM

C,'>'

CALL

163

164

165

166

CALL

GETCH

CO

A.C

LYT

B NCMDS

C CONTAINS LOOP AND INDEX COUNT

167

168 EXECO:

H.CTAB

HL POINTS TO CMND TABLE

CMP

169

COMPARE TABLE ENTRY AND CHARACTER

BRANCH IF EQUAL - CMND RECOGNIZED

ELSE, INCREMENT TABLE POINTER

DECREMENT LOOP COUNT

170

171

172

EXEC1

172

173

174

175 EXEC1:

176

177

178

JNZ

EXECO

BRANCH IF NOT AT TABLE END

ELSE, CMND ILLEGAL - IGNORE IT

EXEC

LXI

LD ADR OF TABLE OF CMND SUBRS

H.CADR

DAD

ADD WHAT IS LEFT OF LOOP COUNT

- EACH ENTRY IN CADR IS 2 BYTES

GET LSP OF ADR OF TABLE ENTRY TO A

POINT TO NXT BYTE IN TABLE

DAD

A,M

H

179

180

MOV

INX

181

182

Н,М

GET MSP OF ADR OF TABLE ENTRY TO H

PUT LSP OF ADR OF TABLE ENTRY TO L

183

184

185

186 ;

D. EXEC

SETUP RETURN ADR ON THE STACK

LXT

; NEXT INSTR COMES FROM CMND SUBR

```

The command and address tables as well as the reading buffer follow to complete the application software.

```

189 :

190

191

COMMAND AND ADDRESS TABLES

192 CTAB:

193

DB

'YSNDETT'

: NUMBER OF VALID COMMANDS

194 NCMDS

F.01

S-CTAB

CADR:

197

198

ETRIC

DW

DW

DW

DW

199

200

201

DTRIG

202

DΨ

NYTRD

202

203

204

205 ;

206 ; RE

207 ;

208 RDBUF:

READING BUFFER AND STACK SPACE

209

210 ;

211

: READING BUFFER

DS

213

END

START

: TRANSFER ADDRESS IS TO START

```

#### SUMMARY/CONCLUSIONS

This instrumentation control application has been presented to demonstrate the simple techniques used to apply the iSBC 80/10A to the task of interfacing instrumentation. A natural extension of this example would include the control of the Fluke 8375 RCU, as well as the control of many additional instruments to build a small ATE system.

1-13 AFN-01931A

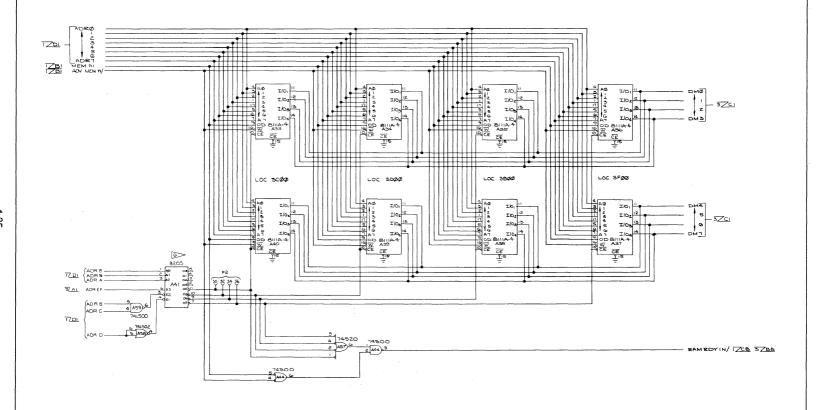

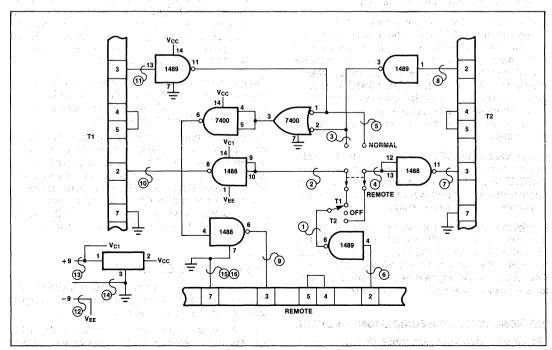

Figure 3. Interface Schematic

#### COMMUNICATION

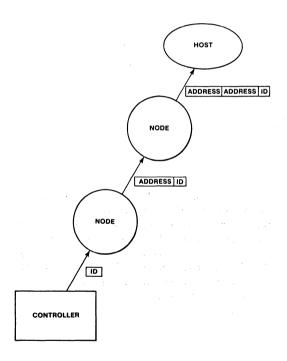

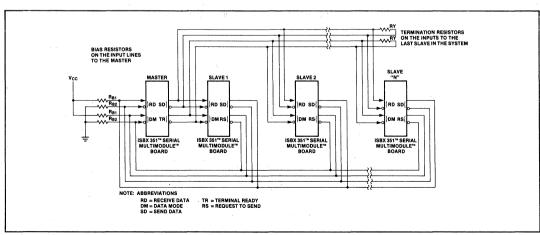

A diverse range of single board computer applications exists in the field of communication. The increase in distributed processing generates requirements for self-contained computers to control elements of a communication system, increasing both the throughput and reliability.

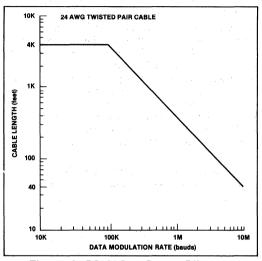

There are many situations that necessitate monitoring and controlling a system from a remote site. Typical examples are systems that cover large geographic areas or systems in dangerous environments for human operators. If the object system, which provides the actual parallel inputs and outputs to the plant, is far from the controlling system, you can lower costs by reducing the number of interconnecting wires via the addition of multiplexers to both systems. In the extreme (and often desirable) case of reducing the interconnects to an absolute minimum, all communication between the systems takes place on a single serial data link. If large distances are involved, this link can be standard telephone wires. For moderate distances, the link can be a single twisted pair. In either case, the equipment used to interface the object system to the serial link is called a supervisory control and data acquisition (SCADA) terminal.

The decision to replace a multitude of interconnects with a SCADA terminal is largely economic. Cables and their associated drivers and receivers can represent a significant part of the total cost of a factory automation project, particularly if an electrically noisy environment requires the use of shielded cables. Any potential savings in cabling must, of course, compensate for the additional cost incurred by adding the SCADA terminal to the system.

#### Communication Application Example

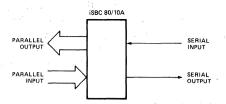

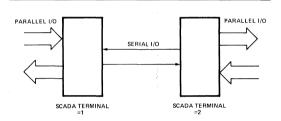

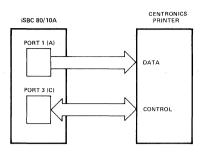

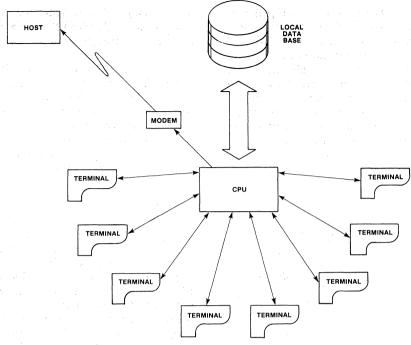

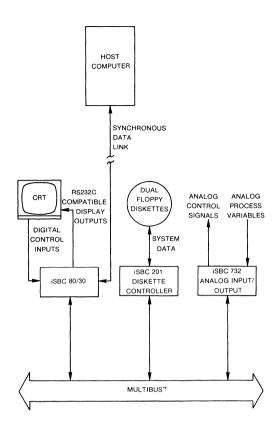

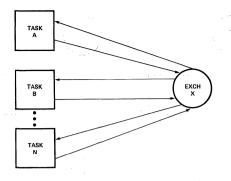

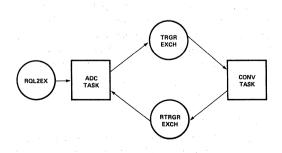

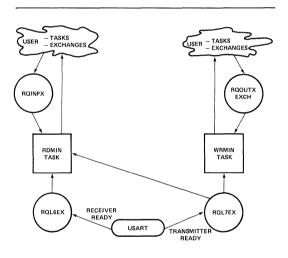

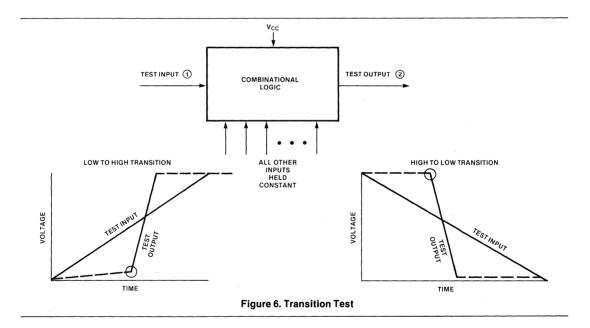

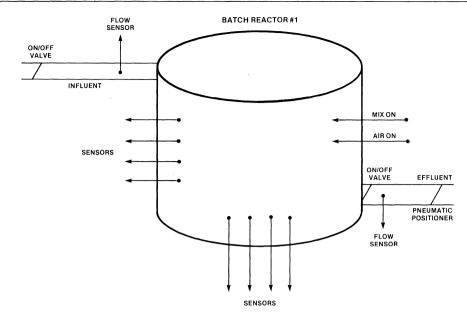

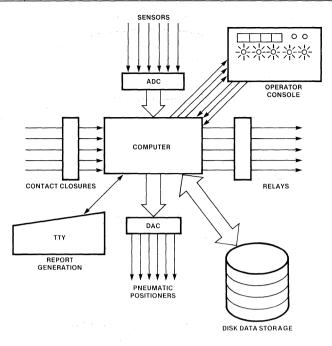

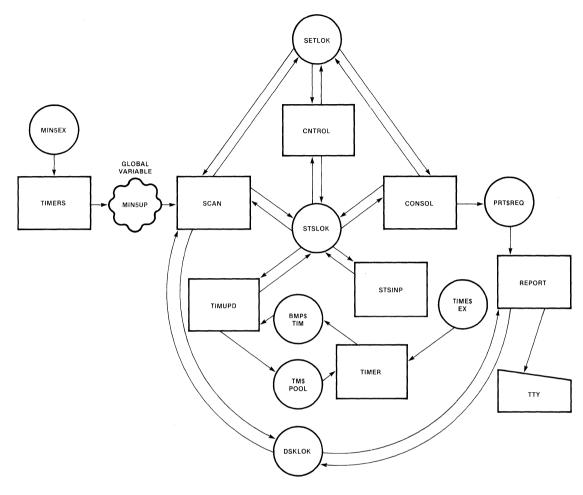

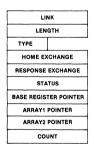

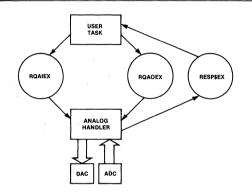

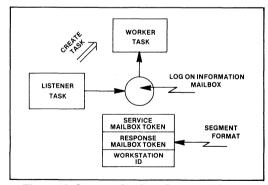

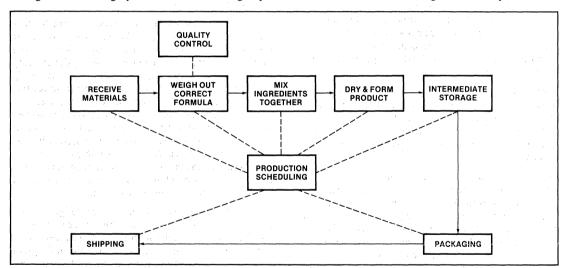

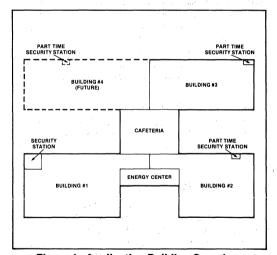

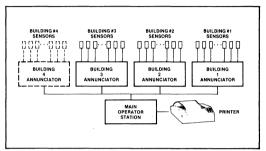

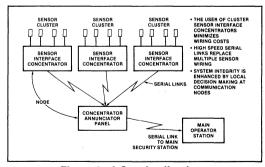

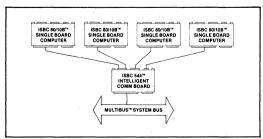

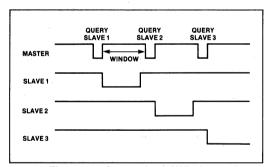

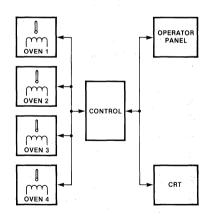

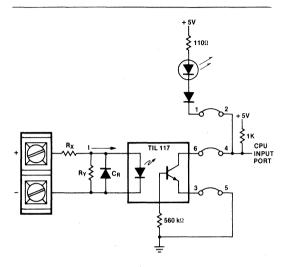

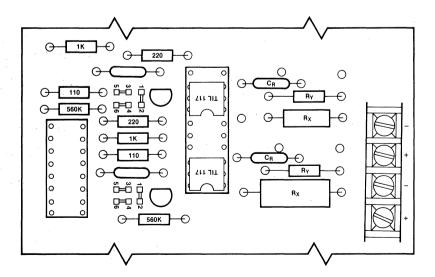

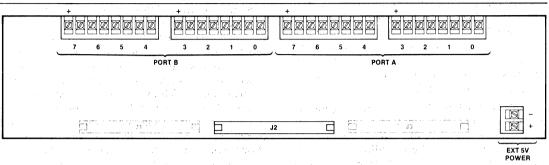

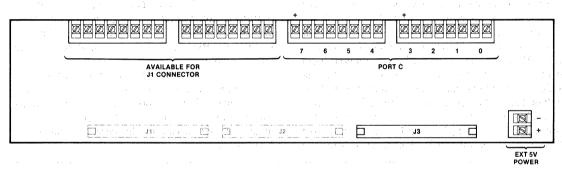

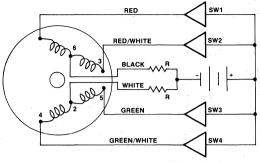

A SCADA terminal demonstrates an industrial communication application of the iSBC 80/10A. The Intel® 8251 USART provides the serial communication link and the two Intel 8255 Programmable Parallel I/O devices provide 48 parallel lines for the object system. A block diagram of a SCADA terminal is shown in Figure 4.

The task of the software in this SCADA terminal example is two-fold. First, it must continually scan its parallel inputs, transmitting the status of those lines in a bit serial mode using the USART. And second, it receives bit serial data from the USART which is to be used to update the parallel outputs. Thus, a major portion of the software deals with

Figure 4. SCADA Terminal Block Diagram

the communications protocol on the serial data lines.

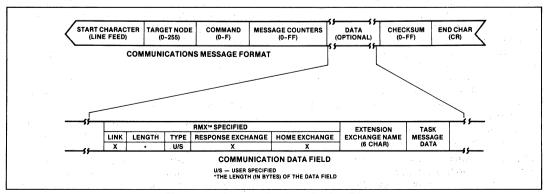

Communications Protocol. A communication protocol is an agreement between communications users that defines the record formats used for data transmissions. The protocol selected for this SCADA terminal application provides the following features:

- 1. A readable character set to simplify the human interface.

- 2. Error detection by means of a checksum.

- Each record specifies the number of data bytes in the record and the initial port number.

Despite its value for human interface, the ASCII character set has problems representing 8-bit binary values, since the high-order bit is not used. Therefore, each binary value is treated as two 4-bit hexadecimal values. Because hexadecimal numbers fall in the range 0–9 and A–F, they can be represented as ASCII characters. However, this representation requires twice as many bytes as a pure binary format.

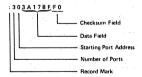

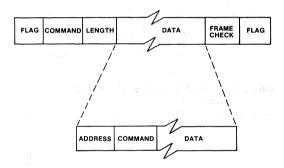

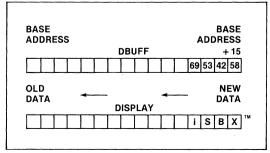

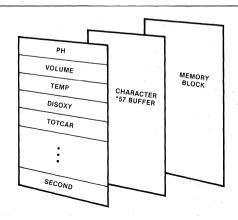

Record Format. The information encoded into the ASCII hexadecimal format is grouped to form records. Each record has a record mark to flag the beginning of the record, a number of ports specification (record length), destination output start port number, the data field itself, and a checksum.

The record format described below is according to the fields in the record.

Record mark field: Byte 0

The ASCII code for a colon (:) is used to signal the start of a record.

Number of ports field: Byte 1

The number of data bytes in the record is represented by a single ASCII hexadecimal digit in this field. This corresponds to the number of 8-bit

1-15 AFN-01931A

ports to which data will be output by the SCADA terminal in a parallel fashion. The maximum number of data bytes in a record is 15 (F in hexadecimal). A record length of zero is a special case and can be reserved for control information.

Port address field: Byte 2

The single ASCII hexadecimal digit in byte 2 gives the port number of the initial output port. The first data byte is output to the port indicated by the port address; successive bytes are output in successive port locations on the iSBC 80/10A or on expansion I/O boards.

Data field: Bytes 3 to 3+2\*(number of ports)-1

An 8-bit binary value is represented by two bytes containing the ASCII characters 0-9 or A-F, which represent a hexadecimal value between 0 and FF (0 and 255 decimal). The high-order digit is in the first byte of each pair.

Checksum field: Bytes 3+2\*(number of ports) to 3+2\*(number of ports)+1

The checksum field contains the ASCII hexadecimal representation of the two's complement of the 8-bit sum of the 8-bit bytes that result from converting each pair of ASCII hexadecimal digits to one byte of binary, from the number of ports field (the number of ports and port address constitute a pair) to and including the last byte of the data field. Therefore, the sum of all the ASCII pairs in a record after converting to binary, from the number of ports field to and including the checksum field, is zero.

Sample Hexadecimal format:

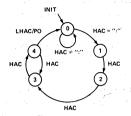

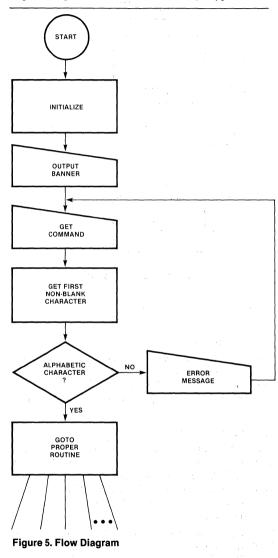

Design Approach Using a State Diagram. Before proceeding to examine the software used to implement the SCADA ferminal, consider how the problem might have been approached with TTL logic rather than a microcomputer. The design would likely have been formulated with a state diagram to specify the transitions of a sequential state machine. The sequential-circuit operations would include decoding the serial input records and

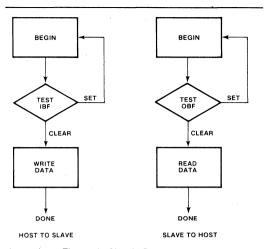

encoding the serial output records. An examination of the serial input record state diagram (Figure 5) is useful in understanding some of the procedures encountered later.

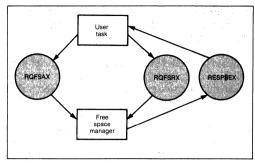

Figure 5. State Diagram

Notes: HAC = Hexadecimal ASCII character

LHAC = Last Hexadecimal ASCII character

PO = Parallel output

The receipt of an invalid HAC will cause a return to state 0.

The receipt of a colon at any time will produce a transition to state 1.

#### STATE DESCRIPTION

0 = record mark state

1 = number of ports state

2 = start port number state

3 = high-order half of data byte state

4 = low-order half of data byte state

State 0 is entered at the time of initialization. All state transitions occur when the next character is received. States 1, 2, and 3 are entered with the input of a colon (:), the number of ports and start port number, respectively. States 3 and 4 will cycle as required until all the high and low-order pairs of data have been input. The transition from state 4 to state 0 occurs when the last data byte has been received. If the checksum is correct, the parallel output latches are loaded with the data field of the record.

There are many references to the states contained in this diagram during the discussion of the software procedures. Thus, the state diagram is used as a "flowchart" for the software. As in the other examples in this application note, a textual description accompanies each segment of code. Intel's high-level programming language, PL/M-80, has been used to show the capability to program in a natural, algorithmic language which eliminates the need to manage register usage or memory allocation.

SCADA Terminal Program. The program begins with a comment, that is followed by the program segment label "SCADA". With resident PL/M-80, all programs are considered to be labelled blocks, or modules. This means that all PL/M programs must begin with a LABEL and a DO statement and end with an END statement.

INDUSTRIAL COMMUNICATION APPLICATION

SCADA TERMINAL

SCADA:

DO;

All variables used in the program must be declared before they can be referred to by their identifiers. This is done by means of a DECLARE statement. In addition to the declaration of variables, macros are declared using the reserved word LITERALLY. These macros are expanded at compile time by textual substitution.

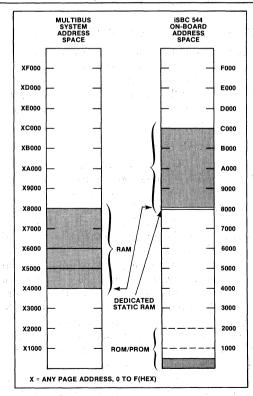

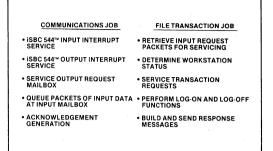

2 1 ARE SRL\$IN\$STATE BYTE, SRL\$IN\$PRT BYTE, SRL\$IN\$CNT BYTE, PRI.\$TN\$STATE BYTE PRL\$IN\$STRT\$PRT BYTE, PRL\$IN\$NMB\$PRTS BYTE, SRL\$IN\$PRL\$OUT\$BFR(3) BYTE, PRL\$OUT\$PRT\$0 LITERALLY '0E5H', PRL\$OUT\$PRT\$1 LITERALLY '0EAH', PRL\$OUT\$PRT\$2 LITERALLY '0E8H', SRL\$OUT\$STATE BYTE, SRL\$OUT\$PRT BYTE, SRL\$OUT\$CNT BYTE. PRL\$OUT\$STATE BYTE, PRL\$OUT\$STRT\$PRT BYTE, PRI \$OUT\$NMB\$PRTS BYTE SRL\$OUT\$PRL\$IN\$BFR(4) BYTE, PRL\$IN\$PRT\$0 LITERALLY '0E4H', PRL\$IN\$PRT\$1 LITERALLY '0E6H' PRL\$IN\$PRT\$2 LITERALLY '0E9H' USARTSCMD LITTERALLY 'OEDH' USART\$MD LITERALLY 'OECH', USART\$OUT LITERALLY 'OECH', USART\$STATUS LITERALLY 'OECH', USART\$MODE\$INSTR LITERALLY 'OCFH', USART\$CMD\$INSTR LITERALLY '025H' TXRDY LITERALLY '001H' RXRDY LITERALLY '002H' PPI\$CWR\$1 LITERALLY '0E7H', PPI\$CWR\$2 LITERALLY 'OEBH', PPI\$CWD\$1 LITERALLY 'O8OH', PPI\$CWD\$2 LITERALLY 'O9BH', TRUE LITERALLY 'OFFH FALSE LITERALLY '000H'. FOREVER LITERALLY 'WHILE TRUE', NEXT\$BYTE BYTE.

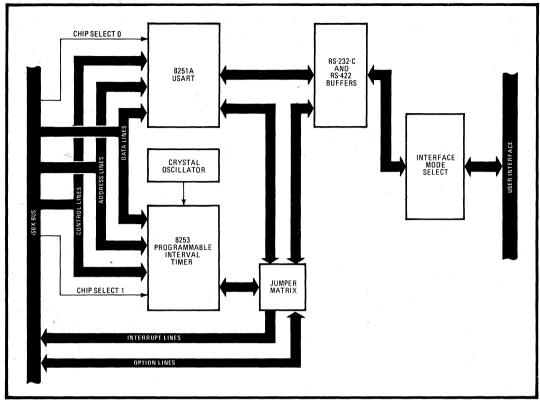

8251 and 8255 Initialization. The INIT procedure sets up the 8251 and 8255's and initializes several variables. Interrupts are disabled to insure that no interrupts are serviced during the execution of the INIT procedure.

- 3 1 INIT: PROCEDURE;

- 4 2 DISABLE;

The serial input and serial output state counters are set to state 0. Port number 0 is the parallel input start port and 3 ports of data are input from the parallel ports for serial transmission.

```

5 2 SRL$IN$STATE = 0;

6 2 SRL$OUT$STATE = 0;

7 2 PRL$IN$STRT$PRT = 0;

8 2 PRL$IN$STRT$PRT = 0;

```

The Intel 8251 USART must be set up by loading it with mode and command instructions.

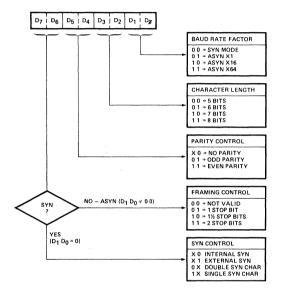

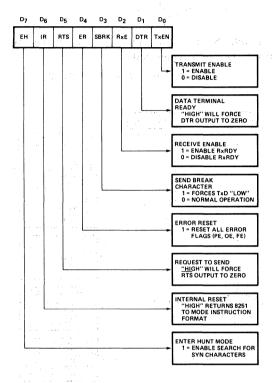

The mode instruction format is shown below:

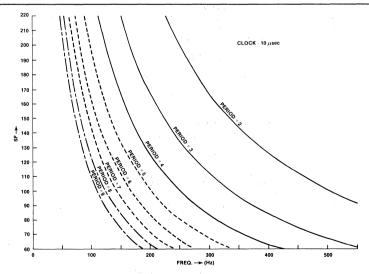

The 8251 characteristics required by this SCADA terminal application include 9600 baud transmission and 8-bit characters. The parallel inputs of the 8255's are periodically scanned. The scanning frequency is determined by the baud rate and number of ports of data being transmitted. For example, the transmission of 3 ports of data requires 11 characters. At a baud rate of 9600 the approximate scan rate is 100 Hz.

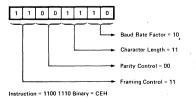

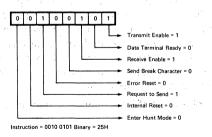

The following 8251 mode instruction is used:

After the mode instruction is sent to the 8251, a command instruction is required to complete the 8251 initialization.

The command instruction format is shown below:

The command instruction enables the transmit and receive functions of the 8251.

The following command instruction is used:

Output instructions send the initialization commands to the 8251. Note that previously declared macros are used to literally replace the mnemonics in the following lines of code.

> OUTPUT(USART\$CMD) = USART\$MODE\$INSTR; OUTPUT(USART\$CMD) = USART\$CMD\$INSTR; 9 2

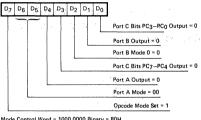

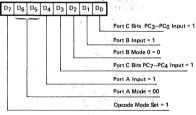

Initialization of the 8255's is then done to set up the following configurations:

8255-#15-50-sub-st-es-6-leading-scale

Port 1 (A) Mode 0 Output Port 2 (B) Mode 0 Output

Port 3 (C) Mode 0 Output

8255 #2

Port 4 (A) Mode 0 Input Port 5 (B) Mode 0 Inbut Port 6 (C) Mode 0 Input

The following command instruction is used for the 8255 #1:

Mode Control Word = 1000 0000 Binary = 80H

The following command instruction is used for the 8255 #2:

Mode Control Word = 1001 1011 Binary = 9BH

The 8255 initialization commands are given in a similar manner to the 8251 commands.

11 2 OUTPUT(PPI\$CWR\$1) = PPI\$CWD\$1; 12 2 OUTPUT(PPI\$CWR\$2) = PPI\$CWD\$2;

The INIT procedure concludes by enabling interrupts.

> 13 2 ENABLE:

Conversion Procedures. Two conversion procedures are required in the program. The first procedure produces a hexadecimal ASCII character from a 4-bit binary value. A typed procedure has been used which returns a value of the type byte. It is called by using its name in an expression.

```

15 1 CHAR$CONV: PROCEDURE (CHAR) BYTE;

16 2 DECLARE CHAR BYTE;

17 2 CHAR = CHAR + '0';

18 2 IF CHAR > '9' THEN

19 2 CHAR = CHAR + 7;

20 2 RETURN CHAR;

21 2 END CHAR$CONV;

```

The second procedure produces a 4-bit binary value from a hexadecimal ASCII character. Because this procedure is used only when a hexadecimal ASCII character is expected, an illegal character (i.e., not a 0–9 or A–F) causes the serial input state counter to indicate state 0. This procedure is also typed. The NMB\$CONV procedure emphatically illustrates the point that PL/M-80 performs unsigned arithmetic. Note that when the ASCII value for a zero is subtracted from the digit, NUM = NUM - '0'; a positive number is always produced, even if the value of NUM is less than '0'.

```

22 1 NMB$CONV: PROCEDURE (NMB) BYTE;

23 2 DECLARE NMB BYTE;

24 2 NMB = NMB - '0';

25 2 IF NNB > 9 THEN

26 2 DO;

27 3 IF (NMB > 16) AND (NMB < 23) THEN

28 3 NMB = NMB - 7;

ELSE

29 3 SRL$IN$STATE = 0;

30 3 END;

31 2 END NMB$CONV:

```

Parallel Input Procedure. A parallel input procedure is used to input data bytes from the 8255's. The data bytes are then transmitted by the bit serial output device. This procedure also computes the checksum for the serial output record. The checksum, TEMP2, is initialized to contain the parallel input number of ports and the start port, shifted to fit within a single byte. Each cycle of the iterative DO block adds the next data byte to the checksum and places the input data into the SRL\$OUT\$PRL\$IN\$BFR array until the loop is complete. The checksum is then computed as the two's complement of the accumulated sum and also stored in the serial input parallel output buffer.

```

33

PARALLELSIN: PROCEDURE:

1

34

2

DECLARE (TEMP1.TEMP2) BYTE:

TEMP2 = PRL$IN$NMB$PRTS * 16 + PRL$IN$STRT$PRT:

35

2

DO PRL$IN$STATE = PRL$IN$STRT$PRT TO

36

2

PRL$IN$STRT$PRT + PRL$IN$NMB$PRTS - 1;

DO CASE PRI.$TN$STATE:

37

3

/* PRL IN PRT 0 */

TEMP1 = INPUT(PRL$IN$PRT$0);

38

/* PRL IN PRT 1 */

TEMP1 = INPUT(PRL$IN$PRT$1);

39

/# PRL IN PRT 2 #/

40

TEMP1 = INPUT(PRL$IN$PRT$2);

111

ш

SRL$OUT$PRL$IN$BFR(PRL$IN$STATE) = TEMP1;

42

43

TEMP2 = TEMP2 + TEMP1:

44

3

45

2

SRI $OUT$PRI $TN$RFR(PRI $TN$STRT$PRT + PRI $TN$NMR$PRTS) = -TEMP2:

2

46

END PARALLELSIN:

```

Parallel Output Procedure. When a complete serial input record has been received and the checksum is correct, the transition from state 4 to state 0 is accompanied by the parallel output of the data from the data field of the serial input record. The parallel output starting port and the number of ports of data is contained in the input record and is thus used in directing the parallel output operation. An iterative DO block increments the PRL\$OUT\$STATE index variable through the required ports and a DO CASE block selectively executes one of the OUTPUT statements for each cycle of the loop.

```

PARALLELSOUT: PROCEDURE;

47

1

DECLARE TEMP BYTE:

DO PRL$OUT$STATE = PRL$OUT$STRT$PRT TO

49

PRL$OUT$STRT$PRT + PRL$OUT$NMB$PRTS - 1;

TEMP = SRL$IN$PRL$OUT$BFR(PRL$OUT$STATE);

50

3

DO CASE PRL$OUT$STATE;

51

/# PRI. OUT PRT 0 #/

52

OUTPUT(PRL$OUT$PRT$0) = TEMP;

/* PRL OUT PRT 1 */

OUTPUT(PRL$OUT$PRT$1) = TEMP;

53

/* PRL OUT PRT 2 */

OUTPUT(PRL$OUT$PRT$2) = TEMP;

54

END:

END PARALLEL$OUT;

```

Serial Input and Output Procedures. The next two procedures contain the software implementations of the state diagram described previously. The processing during each state of the first procedure, the serial character input procedure, is described in the following text.

The procedure begins by reading a character from the 8251 and then converts the character into a 4-bit binary value using the number conversion procedure. The DO CASE block is the mechanism by which a program segment is selected to examine the input character, provide the required outputs, and to specify the transition to the next state.

```

58 1 SERIALSCHARSIN: PROCEDURE;

59 2 DECLARE (CHAR, TDMP) BYTE;

60 2 CHAR = IMPUT(USARTSIN) AND .07FH;

61 2 TEMP = NMBSCONV(CHAR);

62 2 DO CASE SRLSINSSTATE;

```

State 0 is entered through the initialization process, at the completion of the processing of a serial input record, or when an invalid character has been received. The serial input state will remain 0 until a colon (:) is received, at which time a transition to state 1 is specified.

```

/* SRL IN STATE 0 = RECORD MARK */

53 3 DO;

64 4 IF CHAR = ':' THEN

65 4 SRL$IN$STATE = 1;

66 4 END;

```

The parallel output number of ports is obtained, the counter initialized, and a transition to state 2 is specified from state 1.

```

67 3 DO;

68 4 PRL$N$COUT$N$M$$PRTS = TEMP;

69 4 SRL$IN$CNT = TEMP;

70 4 SRL$IN$CNT = 1EMP;

71 4 END;

```

In state 2 the parallel output starting port number is obtained, the serial input port is initialized, the checksum is set to contain the parallel output number of ports and starting port, and a transition to state 3 is specified.

In state 3 the high-order half of a data byte is obtained and shifted into the proper position of the NEXT\$BYTE variable. A transition is specified to state 4.

```

78 SRL IN STATE 3 = HI ORDER HALF DATA BYTE */

DO;

T9 4 NEXT$BYTE = TEMP*16;

80 4 SRL$IN$STATE = 4;

EXD;

```

State 4 is the final state and requires more processing than the others. First, a whole byte of data is assembled by adding the low and high-order data halves, and then testing to determine if the checksum has been received. If so, and the checksum is correct, the parallel output procedure is executed. Once the entire serial input record has been received, a transition is specified to state 0 whether the checksum is correct or not. However, if the

serial input count has not been exhausted, the assembled byte is placed into the serial input parallel output buffer and a transition back to state 3 is specified.

```

/* SRL IN STATE 4 = LO ORDER HALF DATA BYTE */

DO; NEXT$BYTE = NEXT$BYTE + TEMP;

CHECKSIM - CHECKSIM + NEYTARYTE .

IF SRL$IN$CNT = 0 THEN

85

86

87

88

89

90

TE CHECKSOM - O THEN

5 5 5

CALL PARALLEL$OUT;

SRL$IN$STATE = 0;

EI SE

ELSE

OR;

SRL$INSPRL$OUTSBF#(SRL$INSPRT) = NEXT$BYTE;

SRL$INSPRT = SRL$INSPRT + 1;

SRL$INSCAT = SRL$INSCAT - 1;

SRL$INSCATE = 3;

91

92

93

94

95

96

97

END:

98

3

END: /# END OF CASES #/

99

END SERTAL CHARSTN:

```

The serial character output procedure is similar to the serial character input procedure. During state 0 the parallel inputs of the 8255's are stored in the serial output parallel input buffer for transmission.

```

SERIALSCHARSOUT: PROCEDURE:

100

101

2

DECLARE (CHAR, TEMP) BYTE;

CHAR = 0:

102

2

DO CASE SRL$OUT$STATE;

103 . 2

/* SRL OUT STATE 0 : RECORD MARK */

DO;

CHAR = ':';

CALL PARALLEL$IN;

104

105

106

107

SRL$OUT$STATE = 1;

/* SRL OUT STATE 1 = NMB PRTS */

109

110

111

DO;

TEMP = PRL$IN$NMB$PRTS;

SRL$OUT$CNT = TEMP;

SRL$OUT$STATE = 2;

112

END:

/* SRL OUT STATE 2 = STRT PRT */

DO;

TEMP = PRL$IN$STRT$PRT;

115

116

117

118

SRL$OUT$PRT = TEMP;

SRL$OUT$STATE = 3;

END:

/* SRL OUT STATE 3 = HI ORDER HALF DATA BYTE */

DO;

TEMP = SHR(SRL$OUT$PRL$IN$BFR(SRL$OUT$PRT),4);

121

END:

/* SRL OUT STATE 4 = LO ORDER HALF DATA BYTE */

123

124

125

126

EI SE

DO;

SRL$OUT$CNT = SRL$OUT$CNT - 1;

SRL$OUT$PRT = SRL$OUT$PRT + 1;

SRL$OUT$PRT = 3;

127

128

129

130

131

132

END;

END:

133

3

END; /* END OF CASES */

134

IF CHAR <> ':' THEN

135

136

CHAR = CHAR$CONV(TEMP):

2

OUTPUT(USART$OUT) = CHAR;

137

END SERIALSCHARSOUT:

```

Interrupt Service Routine. The software in this SCADA terminal application example is interrupt driven. Interrupts, which occur when the transmitter of the 8251 is ready for another character of when the receiver has obtained a serial character, direct the execution of either the serial input

or output character procedures. The following procedure is entered when an interrupt occurs.

```

138 1 USART$INTERRUPT: PROCEDURE INTERRUPT 7;

139 2 DECLARE STATUS BYTE;

140 2 STATUS = INPUT(USART$STATUS);

141 2 IF (STATUS AND TXRDY) = TXRDY THEN

CALL SERIALSCHAR$OUT;

143 2 IF (STATUS AND RXRDY) = RXRDY THEN

CALL SERIALSCHAR$IN;

145 2 END USART$INTERRUPT;

```

Main Program. The function of the main program is rather simple. It calls the initialization routine and then loops "FOREVER." Notice that the other software is executed only when an interrupt occurs. Rather than loop idly while waiting for an interrupt, the "main program" could take advantage of excess CPU time by processing some other task.

|            |     | /*******            |

|------------|-----|---------------------|

|            |     | MAIN\$PROGRAM:      |

|            |     | *********/          |

| 146        | 1   | CALL INIT;          |

| 147<br>148 | 1 2 | DO FOREVER;<br>END; |

149 1 END;

#### SUMMARY/CONCLUSIONS

Further consideration should be given to error checking in the implementation of a SCADA terminal. A checksum has been used in this example which provides some error detection but no correction.

The industrial communication example in this application note has shown a SCADA terminal. Besides providing a convenient forum in which to explore the use of PL/M in an interrupt-driven environment, this application provides a realistic and almost fully-developed tool for the replacement of a multitude of parallel lines. Two such systems can be connected through the serial lines to provide a parallel to parallel transmission scheme as shown in Figure 6.

Figure 6. Two SCADA Terminals

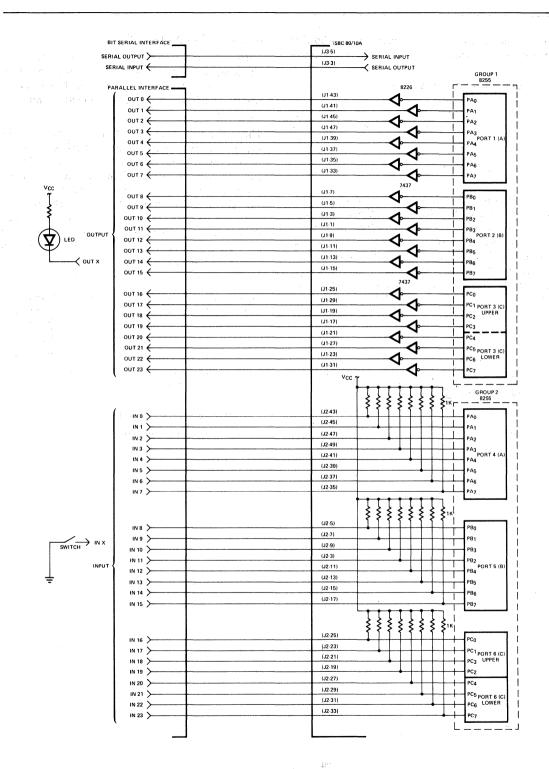

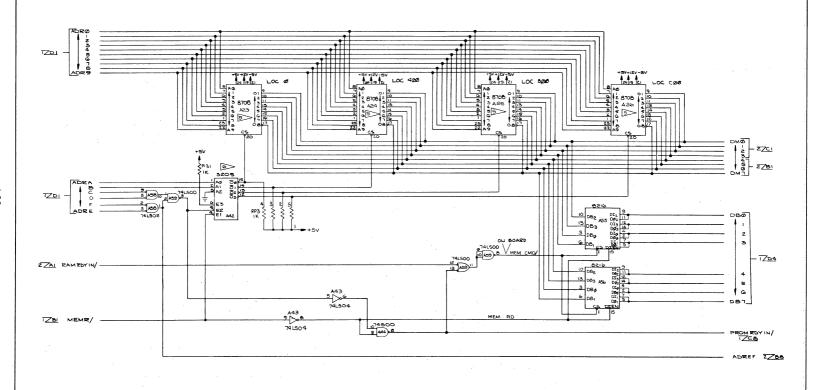

Figure 7. SCADA Terminal Schematic

#### PROCESS CONTROL

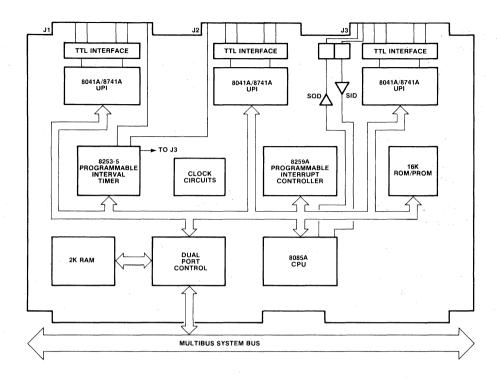

Many single board computers have already been applied in the field of process control. Some of the common denominators observed in these applications include the use of A/D and D/A peripheral boards, process monitoring functions such as servicing display panels for operator interaction, and alarm indicators.

#### **Temperature Monitoring Application Example**

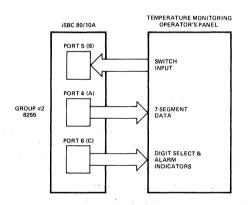

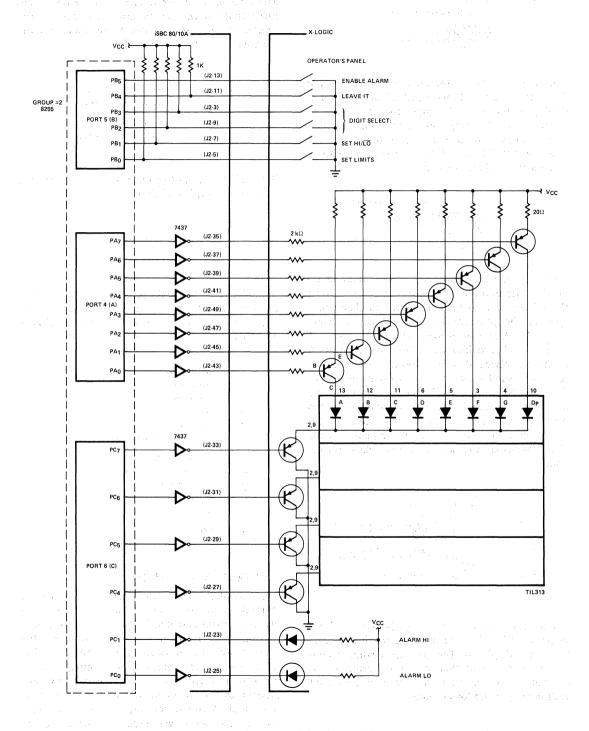

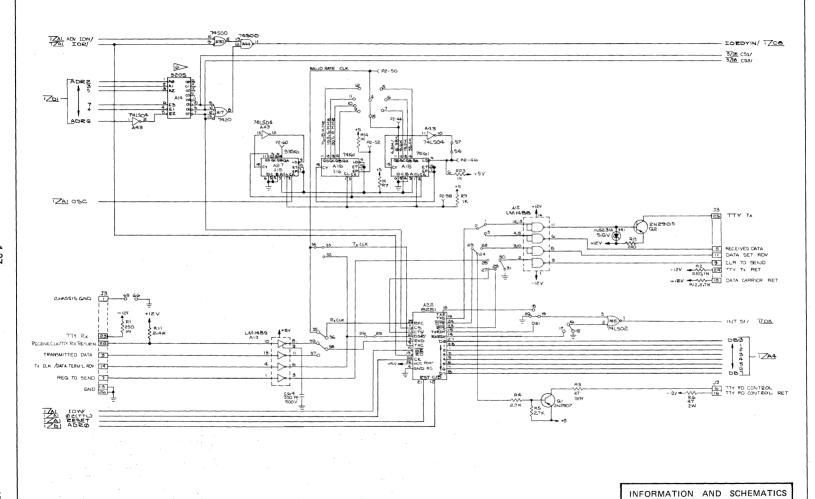

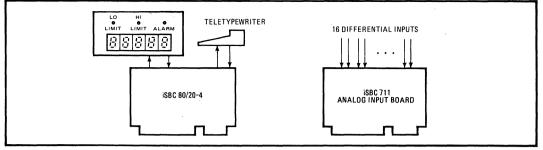

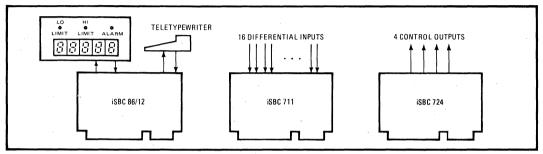

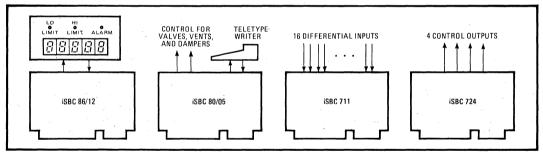

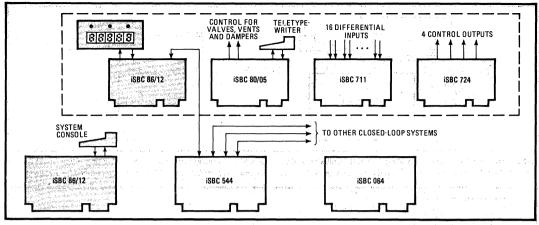

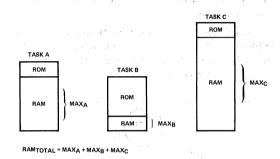

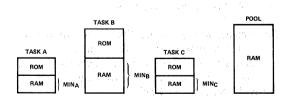

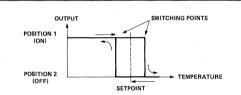

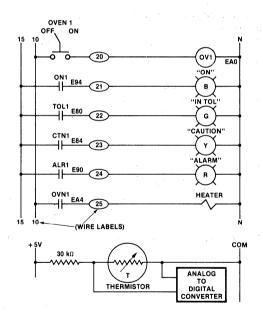

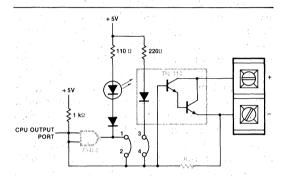

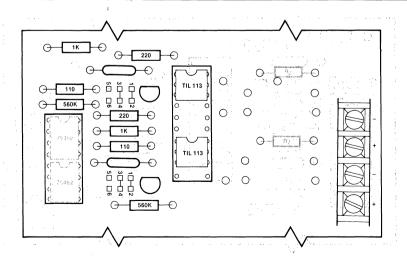

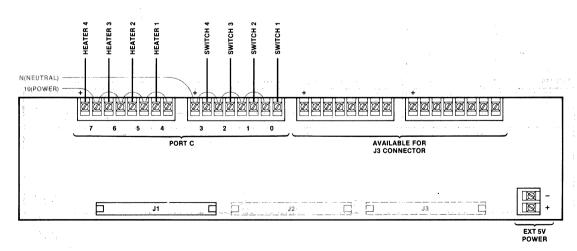

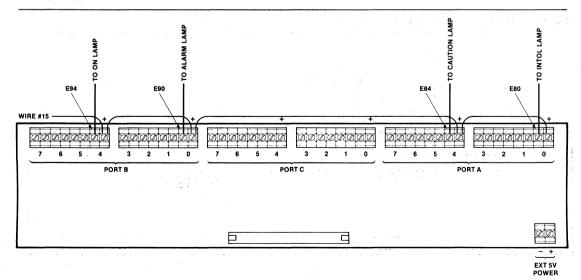

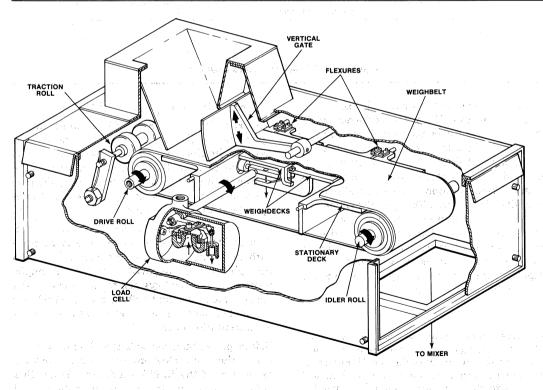

A temperature monitoring system has been developed for the purposes of a process control application example. The single open loop system utilizes an A/D converter, a multiplexed display, switches for operator control, and two alarms. A block diagram of the operator's panel is shown in Figure 8 and a schematic in Figure 9.

Figure 8. Operator's Panel Block Diagram

Operator's Panel. The operator's panel in this temperature monitoring system contains four 7-segment displays to show the temperature, two light emitting diodes (LEDs) that indicate alarmlow and alarm-high conditions, and six switches. The function of the switches is as follows:

Set Limit — controls whether the current temperature reading is to be displayed (off) or if upper/lower limits are to be set (on).

Set Hi Lo — when set limit is "on", this switch controls whether the low (off) or high (on) limit is to be displayed.

Digit Selects — these two switches control the selection of the digit of the limit which is to be modified. The four binary positions 00, 01, 10 and 11 correspond to the four 7-segment digits.

Leave It — controls whether the digit selected is to be incremented (off) or maintained at its current value (on). When this switch is "off" the digit selected is incremented every 512 ms until the operator turns the switch "on".

Enable Alarm — when set limit is "off" and the current temperature is displayed, this switch controls whether the action of the alarm indicators is to be enabled (on) or disabled (off).

The simple means used to set upper and lower temperature limits is similar to setting the time on a digital wrist watch.

The purpose of the software is to initialize the system and then to enter an endless loop which accumulates 16 readings, updates the displayed reading or handles limit setting, updates the display latches, waits 4 ms, and obtains an A/D reading.

Temperature Monitoring Program. This application example has been coded in Intel's resident PL/M-80 language.

PROCESS CONTROL APPLICATION

OPEN LOOP

TEMPERATURE MONITOR

\*/

TEMPERATURE\$MONITOR:

DO;

The declaration statement includes some dimensioned variables with INITIAL attributes. They provide data strobe positions, a table of bit patterns to convert BCD data to 7-segment data, and a table of the powers of 10 for binary to BCD conversions.

PECLARE

READING ADDRESS,

DIGITS(4) BYTE INITIAL (30H, 40H, 20H, 10H),

BCDTOYSEG(11) BYTE INITIAL (37H, 05H, 58H, 4FH, 66H,

60H, 70H, 77H, 67H, 07),

TENS(4) ADDRESS INITIAL (1000, 100, 10, 10, 1),

DIGITSDATA(4) BYTE,

NYTSDIGIT BYTE,

UPDATESCOUNT BYTE,

LIMIT(2) ADDRESS,

ACCUMSROMG ADDRESS,

ACCUMSROMG ADDRESS,

CUR LITERALLY '06BH',

SCOS LITERALLY '06BH',

SCOS LITERALLY '06BH',

STELLIMIT LITERALLY '00CH',

STELLIMIT LITERALLY '07H',

STENHISLO LITERALLY '07H',

STENHISLO LITERALLY '07H',

STENHISLO LITERALLY '07H',

STENALARMSHO LITERALLY '07H',

STENALARMSHO LITERALLY '07H',

RESETSALARMSHO LITERALY '07H',

RESETSALARMSHO RESETSAL RES

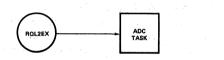

The analog to digital conversion procedure has been coded in assembly language and is not included in this application note. It is declared as an external typed procedure with no arguments and returns a value of the type address. The value returned is the current temperature. The ATOD procedure is linked later in a step to produce an absolute load module of the entire program.

```

3 1 ATOD: PROCEDURE ADDRESS EXTERNAL;

4 2 END ATOD:

```

Bit set/reset functions of the 8255 have been used to control the alarm-low and high output bits. Use of this function allows individual bits to be controlled without affecting others of port C which are concurrently selecting the digit to be multiplexed on the display.

```

5 1 RESET$ALARMS: PROCEDURE;

6 2 OUTPUT(CWR) = RESET$ALARM$LO;

7 2 OUTPUT(CWR) = RESET$ALARM$HI;

6 2 END RESET$ALARM$H;

```

The following procedure is used to initialize the 8255 and several program variables.

```

9 1 INIT: PROCEDURE;

10 2 OUTPUT(CMR) = SETUP$PORTS;

11 2 CALL RESET$ALARMS;

12 2 WIN$1011 = 0;

13 2 UPDATE$COUNT = 0;

14 2 SET$COUNT = 7;

15 2 READING = 0;

16 2 ACCUM$ROND = 0;

17 2 LIMIT(0) = 0000;

18 2 LIMIT(1) = 9999;

19 2 END INIT;

```

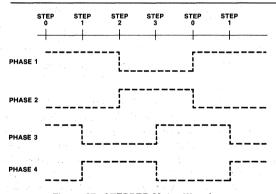

A multiplexed display is controlled by the software. Two ports of an 8255 are required for this function shown in Figure 9. The first output port holds the data which drives the four 7-segment displays in parallel. The second output port contains four strobes, each going to a separate common cathode of one of the 7-segment displays.

The update display procedure begins by blanking 7-segment data in the output port. This step avoids shadows that would be produced if the data for the next digit position were loaded prior to updating the strobe. The strobe is then advanced, retaining the alarm bits that occupy other bits of the same output port. Note that an output configured 8255 port can be read with an 8080A INPUT instruction to determine the currently latched output data. The BCD data is obtained from the next digit position of the DIGIT\$DATA array and used as a subscript into a table of BCDTO7SEG data. The 7-segment data is also

output to the 8255 port in the same statement. The procedure concludes by advancing the NXT\$DIGIT pointer.

```

20 1 DISPLATSUPDATE: PROCEDURE;

21 2 OUTPUT(SEGS) = 0;

22 2 OUTPUT(SECT) = (DIGITS(NXTSDIGIT) OR (INPUT(SLCT) AND 03H));

23 2 OUTPUT(SEGS) = BCDTOTSGG(DIGITSDATA(NXTSDIGIT));

24 2 NXTSDIGIT = (NXTSDIGIT+1) AND 03H;

25 2 END DISPLATSUPPATE:

```

Binary to BCD Conversion. Binary data from the A/D converter must be converted to BCD before it can be used by the DISPLAY\$UPDATE procedure to show the current temperature reading. The BINTOBCD procedure performs this conversion operation.

```

1

26

BINTORCD: PROCEDURE:

27

DECLARE (BCD,I) BYTE;

2

DO I = 0 TO 3:

28

BCD = 0;

DO WHILE READING >= TENS(I):

30

READING = READING - TENS(I);

BCD = BCD + 1;

33

Ш

END:

34

3

DIGIT$DATA(I) = BCD;

35

3

END:

36

END BINTOBCD:

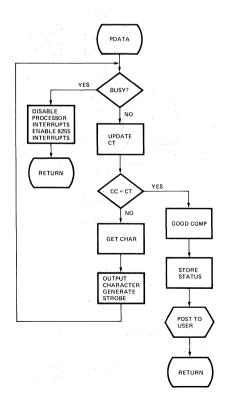

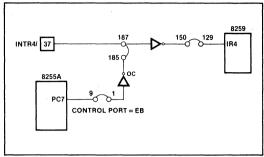

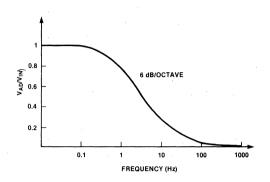

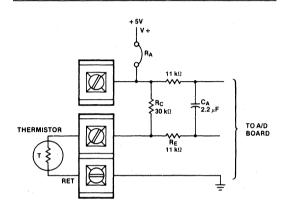

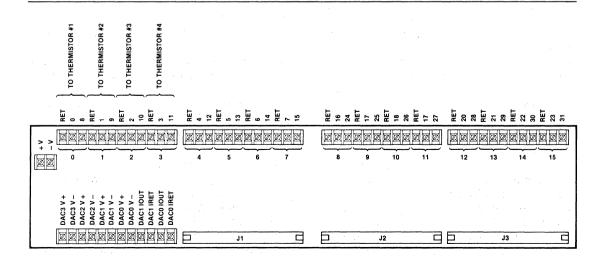

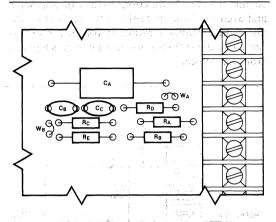

```